# 8 Channels, 8-Bit Digital-to-Analog Converter with Output Operational Amplifier

#### GENERAL DESCRIPTION

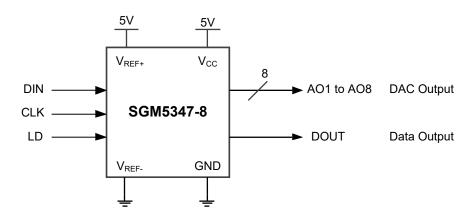

The SGM5347-8 features 8 channels of 8-bit digital-toanalog converter (DAC) with output amplifiers. The output amplifier provides high current drive capability. The digital data is input via a serial link bus. Only three control lines are required, and cascaded connections can be used.

The SGM5347-8 is suitable for electronic volume control and replacement for potentiometers for adjustment, in addition to normal DAC applications.

The SGM5347-8 is available in Green SOIC-16 and TSSOP-16 packages. It operates over an ambient temperature range of -40°C to +125°C.

#### **FEATURES**

- Low Power Consumption (0.5mW/CH)

- Integrating 8 Channels of 8-Bit DAC

- Simultaneous 8 Channels Output Updating

- Build-in Analog Output Amplifier with Sink/Source Current Capability and Short Current Control

SGM5347-8

- The Range of D/A Conversion can be Independently Set by Separating the Power Supply for MCU Interface and Operational Amplifier and the Power Supply for DAC

- Capable of being Controlled Directly by a 3V MCU

- Individual Channel Power-Down Capability

- 0.6µA (TYP) I<sub>CC</sub> for Power-Down Mode

- Power-On Reset: Output Reset to GND

- Daisy-Chain Capability

- Serial Data Input: Up to 2.5MHz Operation

- Wide Power Supply Range: 2.8V to 5.5V

- Available in Green SOIC-16 and TSSOP-16 Packages

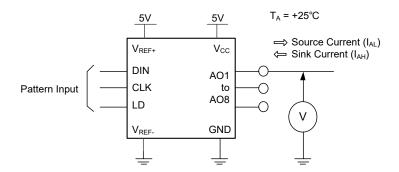

#### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |  |

|-----------|------------------------|-----------------------------------|--------------------|----------------------------|---------------------|--|

| SCME247.0 | SOIC-16                | -40°C to +125°C                   | SGM5347-8XS16G/TR  | SGM53478XS16<br>XXXXX      | Tape and Reel, 2500 |  |

| SGM5347-8 | TSSOP-16               | -40°C to +125°C                   | SGM5347-8XTS16G/TR | SGM53478<br>XTS16<br>XXXXX | Tape and Reel, 4000 |  |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage Range (1)         |                         |

|----------------------------------------|-------------------------|

| V <sub>CC</sub>                        | 0.3V to 6.5V            |

| V <sub>REF+</sub>                      | 0.3V to 6.5V            |

| V <sub>REF</sub>                       | GND ± 0.3V              |

| Input Voltage Range, V <sub>IN</sub>   | 0.3V to $V_{CC}$ + 0.3V |

| Output Voltage Range, V <sub>OUT</sub> | 0.3V to $V_{CC}$ + 0.3V |

| Package Thermal Resistance             |                         |

| SOIC-16                                | 90°C/W                  |

| TSSOP-16                               | 120°C/W                 |

| Junction Temperature                   | +150°C                  |

| Storage Temperature Range              | 65°C to +150°C          |

| Lead Temperature (Soldering, 10s)      | +260°C                  |

| ESD Susceptibility                     |                         |

| HBM                                    | 4000V                   |

| CDM                                    | 1000V                   |

|                                        |                         |

NOTE: 1.  $V_{CC} \ge V_{REF+}$ .

#### RECOMMENDED OPERATING CONDITIONS

| Operating Temperature Range40                                         | °C to +125°C            |

|-----------------------------------------------------------------------|-------------------------|

| Power Supply Voltage 1                                                |                         |

| V <sub>CC</sub>                                                       | 2.8V to 5.5V            |

| GND                                                                   | 0V                      |

| Power Supply Voltage 2 (V <sub>REF+</sub> - V <sub>REF-</sub> ≥ 0.5V) |                         |

| V <sub>REF+</sub>                                                     | 0.5V to V <sub>CC</sub> |

| V <sub>REF-</sub>                                                     | GND                     |

| Oscillation Limited Output Capacitance, $C_{\text{OL}}$               | 2nF (TYP)               |

| Digital Data Setting Range                                            | #00 to #FF              |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

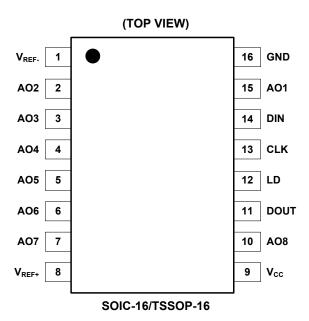

#### **PIN CONFIGURATIONS**

#### **PIN DESCRIPTION**

| PIN                         | NAME              | TYPE | FUNCTION                                                                                                                                           |

|-----------------------------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                           | $V_{REF}$         | -    | Negative Reference Voltage Input. Always connect this pin to ground in application.                                                                |

| 8                           | V <sub>REF+</sub> | -    | Positive Reference Voltage Input.                                                                                                                  |

| 9                           | V <sub>CC</sub>   | -    | Power Supply Pin. Power supply pin of MCU interface and operational amplifier.                                                                     |

| 16                          | GND               | -    | Ground Pin. Ground pin of MCU interface and operational amplifier.                                                                                 |

| 15, 2, 3, 4,<br>5, 6, 7, 10 | AO1-AO8           | 0    | DAC Output Pins. These pins are 8-bit DAC outputs with operational amplifiers.                                                                     |

| 11                          | DOUT              | 0    | Data Output Pin. This pin outputs MSB of the 12-bit shift register.                                                                                |

| 12                          | LD                | I    | Load Signal Input Pin. If LD pin is brought from low to high, the data of shift register is loaded to the decoder and the register for DAC output. |

| 13                          | CLK               | I    | Shift Clock Input Pin. The input signal from the DIN pin is input to a 12-bit shift register on the rising edge of the shift clock.                |

| 14                          | DIN               | I    | Serial Data Input Pin. This pin inputs 12-bit length serial data.                                                                                  |

NOTE: DIN, CLK, and LD pins should remain "L" level at non-data transfer.

### **ELECTRICAL CHARACTERISTICS**

( $V_{CC}$  = 2.8V to 5.5V,  $T_A$  = -40°C to +125°C,  $V_{REF+}$  =  $V_{CC}$ ,  $V_{REF-}$  = GND,  $C_L$  = 200pF to GND, input code range from 3 to 252. Typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                     | CONDITIONS                        | MIN   | TYP | MAX             | UNITS         |  |

|-------------------------------|-----------------------------------|-------|-----|-----------------|---------------|--|

| Analog DC Performance         |                                   |       |     |                 |               |  |

| Resolution                    |                                   | 8     |     |                 | Bit           |  |

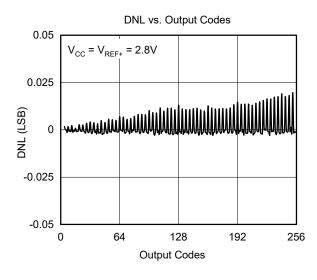

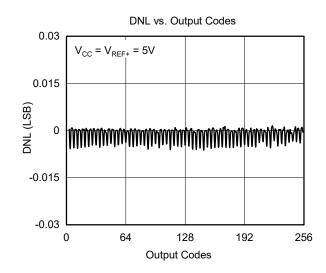

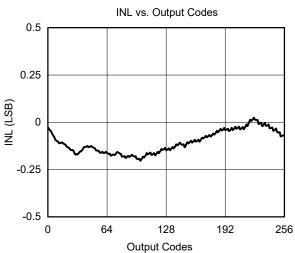

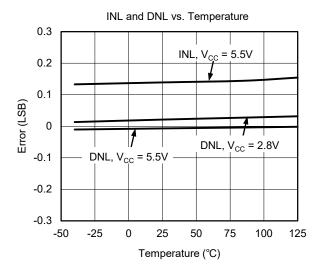

| INL (1)                       |                                   |       | 0.2 | 0.7             | LSB           |  |

| DNL (2)                       | Monotonicity guaranteed by design | -0.15 |     | 0.2             | LSB           |  |

| Offset                        |                                   |       | 3   | 15              | mV            |  |

| Gain Error                    |                                   |       | 0.1 | 0.45            | %FSR          |  |

| Offset Drift                  |                                   |       | 10  | 60              | μV/°C         |  |

| Gain Drift                    |                                   |       | 2   | 15              | ppmFS/°C      |  |

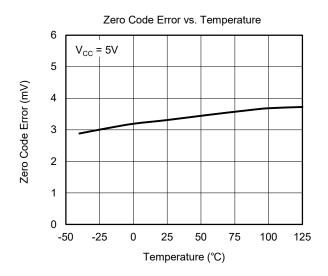

|                               | 0μA current load                  |       | 3   | 15              |               |  |

| Zero Code Error               | 200μA current load                |       | 5   |                 | mV            |  |

|                               | 1mA current load                  |       | 8   |                 |               |  |

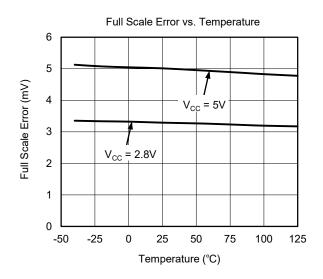

|                               | 0μA current load                  |       | 3   | 35              |               |  |

| Full Scale Error              | 200μA current load                |       | 6   |                 | mV            |  |

|                               | 1mA current load                  |       | 20  |                 |               |  |

| Zero Code Drift               |                                   |       | 5   |                 | μV/°C         |  |

| Full Scale Error Drift        |                                   |       | 5   |                 | μV/°C         |  |

| Analog AC Performance         |                                   | l     |     | ı               |               |  |

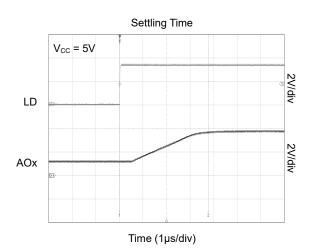

| Output Settling Time          | To 1LSB                           |       | 7   |                 | μs            |  |

| Slew Rate                     | C <sub>LOAD</sub> = 200pF         |       | 0.9 |                 | V/µs          |  |

| Noise Density                 | Code = 0x80, f = 1kHz             |       | 30  |                 | nV/√Hz        |  |

| Noise                         | 30kHz LPF                         |       | 17  |                 | $\mu V_{RMS}$ |  |

| Multiplying Bandwidth         |                                   |       | 300 |                 | kHz           |  |

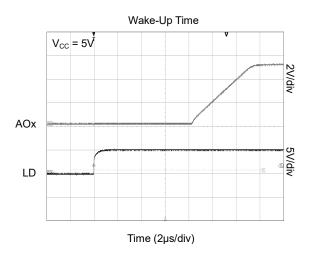

| Wake-Up Time                  | C <sub>LOAD</sub> = 200pF         |       | 8   |                 | μs            |  |

| Output Characteristics        |                                   | l .   |     | · L             | -             |  |

| Output Resistance             |                                   |       | 0.3 |                 | Ω             |  |

| ·                             | Sink                              |       | 37  |                 |               |  |

| Short Current                 | Source                            |       | 37  |                 | mA            |  |

| (2)                           | V <sub>cc</sub> = 2.8V            |       | 5   |                 |               |  |

| Continuous Current (3)        | V <sub>cc</sub> = 5.5V            |       | 10  |                 | mA            |  |

| Maximum Capacitance Load      |                                   |       | 2   |                 | nF            |  |

| Reference Characteristics     |                                   | l     |     | ı               |               |  |

| V <sub>REF+</sub>             |                                   | 0.5   |     | V <sub>CC</sub> | V             |  |

| Input Impedance               |                                   |       | 25  |                 | kΩ            |  |

| Digital Input Characteristics |                                   | l     |     | ı               |               |  |

| Input Current                 |                                   |       | 0.1 | 1               | μA            |  |

| •                             | V <sub>CC</sub> = 2.8V to 3.6V    |       |     | 0.6             |               |  |

| Input Low Voltage             | V <sub>CC</sub> = 4.5V to 5.5V    |       |     | 0.8             | V             |  |

|                               | V <sub>CC</sub> = 2.8V to 3.6V    | 2.3   |     |                 |               |  |

| Input High Voltage            | V <sub>CC</sub> = 4.5V to 5.5V    | 3.5   |     |                 | V             |  |

| Input Hysteresis              |                                   |       | 0.2 |                 | V             |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.8V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, V_{REF+} = V_{CC}, V_{REF-} = GND, C_L = 200pF \text{ to GND, input code range from 3 to 252.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER             |                   | CONDITIONS                                                      | MIN | TYP  | MAX  | UNITS |  |  |  |

|-----------------------|-------------------|-----------------------------------------------------------------|-----|------|------|-------|--|--|--|

| Power-On Reset        |                   |                                                                 |     |      |      |       |  |  |  |

| Reset Level           |                   | MIN for minimum entry level, MAX for maximum release level 2.45 |     | 2.6  | 2.78 | V     |  |  |  |

| Hysteresis            |                   | Difference between reset release level and entry level          |     |      |      | mV    |  |  |  |

| Power Consumption     |                   |                                                                 |     |      |      |       |  |  |  |

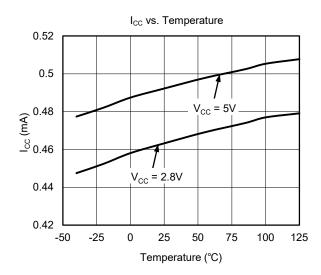

| Normal Operation Made | Icc               | V <sub>CC</sub> = 5V                                            |     | 0.5  | 0.8  | m A   |  |  |  |

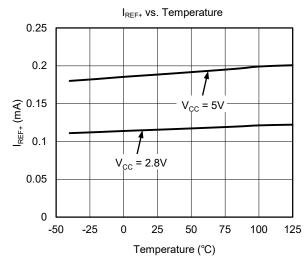

| Normal Operation Mode | I <sub>REF+</sub> | V <sub>REF+</sub> = 5V                                          |     | 0.2  | 0.4  | mA    |  |  |  |

| Power-Down Mode       |                   | V <sub>CC</sub> = 5V                                            |     | 0.6  | 3    |       |  |  |  |

|                       |                   | V <sub>REF+</sub> = 5V                                          |     | 0.01 | 1    | μΑ    |  |  |  |

#### NOTES

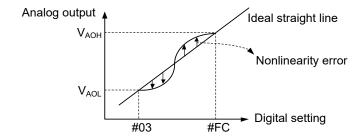

- 1. Nonlinearity error: The error of the I/O curve deviated from the ideal straight line between output voltages at "#03" and "#FC".

- 2. Differential nonlinearity error: The error deviated from the ideal increment given when the digital value is incremented by one bit.

- 3. At +125°C, please limit the output current of each channel to 5mA for maximum operating life time.

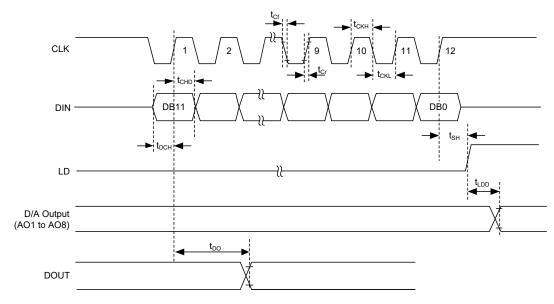

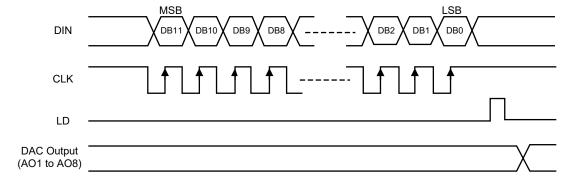

#### **TIMING CHARACTERISTICS**

( $V_{CC}$  = 2.8V to 5.5V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                      | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| "L" Level Clock Pulse Width                    | t <sub>CKL</sub> |            | 200 |     |     | ns    |

| "H" Level Clock Pulse Width                    | t <sub>CKH</sub> |            | 200 |     |     | ns    |

| Clock Rising Time                              | t <sub>Cr</sub>  |            |     |     | 200 | no    |

| Clock Falling Time                             | t <sub>Cf</sub>  |            |     |     | 200 | ns    |

| Data Setup Time                                | t <sub>DCH</sub> |            | 30  |     |     | ns    |

| Data Hold Time                                 | t <sub>CHD</sub> |            | 60  |     |     | ns    |

| Load Setup Time                                | t <sub>CHL</sub> |            | 200 |     |     | ns    |

| Load Hold Time                                 | t <sub>LDC</sub> |            | 100 |     |     | ns    |

| "H" Level Load Pulse Width                     | t <sub>LDH</sub> |            | 100 |     |     | ns    |

| Data Output Delay Time                         | t <sub>DO</sub>  |            | 70  |     | 350 | ns    |

| D/A Output Settling Time                       | t <sub>LDD</sub> |            |     |     | 100 | μs    |

| LD Hold Time after the 12th Rising Edge of CLK | t <sub>SH</sub>  |            | 60  |     |     | ns    |

#### NOTES:

- 1. The D/A output evaluation levels are 90% and 10% of  $V_{CC}$ . The other evaluation levels are 80% and 20% of  $V_{CC}$ . 2. Please ensure of the 12 bits of data are sent before the rising edge of LD.

Figure 2. Input/Output Timing

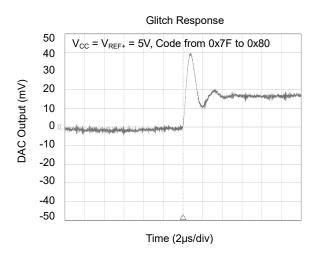

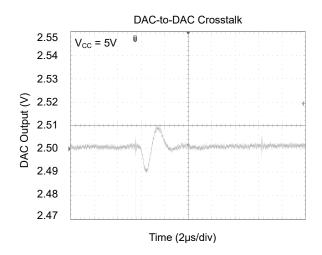

#### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A$  = +25°C, unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C, unless otherwise noted.

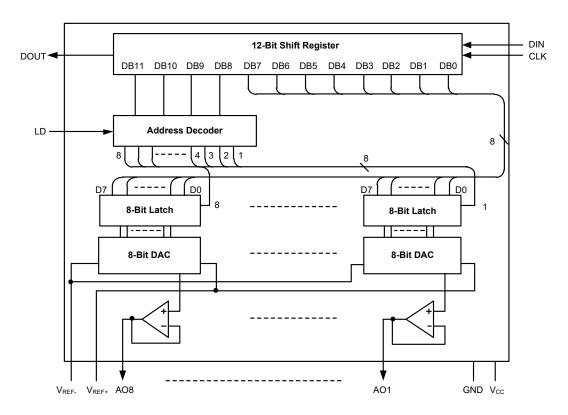

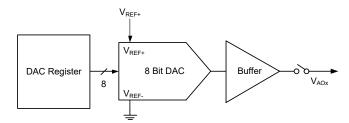

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Block Diagram

#### TIMING CHART AT DATA SETTING

Figure 4. Timing Chart at Data Setting

#### **DETAILED DESCRIPTION**

#### **DAC Architecture**

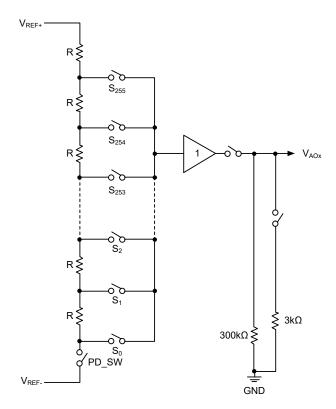

The SGM5347-8 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings followed by an output buffer. The reference voltage is externally applied at  $V_{\text{REF+}}$  for DAC channels 1 through 8.

For simplicity, a single resistor string is shown in Figure 5. This string consists of 256 equal valued resistors with a switch at each junction of two resistors, plus a switch to ground. The code loaded into the DAC register determines which switch is closed, connecting the proper node to the amplifier. The input coding is straight binary with an ideal output voltage of:

$$V_{AOx} = D \times V_{LB} + V_{REF}$$

(1)

$$V_{LB} = (V_{REF+} - V_{REF-})/256$$

(2)

where

D is the decimal equivalent of the binary code that is loaded into the DAC register.

D can take on any value between 0 and 255. This configuration ensures that the DAC is monotonic.

Figure 5. DAC Resistor String

Because all 8 DAC channels of the SGM5347-8 can be controlled independently, each channel consists of a DAC register and an 8-bit DAC. Figure 6 is a simple block diagram of an individual channel in the SGM5347-8. Depending on the mode of operation, data written into a DAC register causes the 8-bit DAC output to be updated, or an additional command is required to update the DAC output. Further description of the mode of operation can be found in CONTROL Register section.

Figure 6. Single-Channel Block Diagram

### **DETAILED DESCRIPTION (continued)**

#### **Data for Shift Register**

- SGM5347-8 has a 12-bit shift register for chip control.

- It is necessary to set the data as following configuration to a 12-bit shift register.

- The data consists of 12 bits: a 4-bit address selection and an 8-bit DAC control signal.

|      |          | Address Selection Signal |      |     |     | DAC Control Signal |     |     |     |     |     |     |         |          |     |

|------|----------|--------------------------|------|-----|-----|--------------------|-----|-----|-----|-----|-----|-----|---------|----------|-----|

| DOUT | <b>←</b> | DB11                     | DB10 | DB9 | DB8 | DB7                | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0     | <b>←</b> | DIN |

|      |          | 1 <sup>st</sup> in       |      |     |     |                    |     |     |     |     |     |     | Last in |          |     |

Figure 7. Serial Data

8-Bit DAC

#### **Address Selection Signal**

|      | Input Da | ta Signal |     | Address Selected |

|------|----------|-----------|-----|------------------|

| DB11 | DB10     | DB9       | DB8 | Address Selected |

| 0    | 0        | 0         | 0   | Don't care.      |

| 1    | 0        | 0         | 0   | AO1 selected.    |

| 0    | 1        | 0         | 0   | AO2 selected.    |

| 1    | 1        | 0         | 0   | AO3 selected.    |

| 0    | 0        | 1         | 0   | AO4 selected.    |

| 1    | 0        | 1         | 0   | AO5 selected.    |

| 0    | 1        | 1         | 0   | AO6 selected.    |

| 1    | 1        | 1         | 0   | AO7 selected.    |

| 0    | 0        | 0         | 1   | AO8 selected.    |

| 1    | 0        | 0         | 1   | PWR_DWN.         |

| 0    | 1        | 0         | 1   | CONTROL.         |

| 1    | 1        | 0         | 1   | Don't care.      |

| 0    | 0        | 1         | 1   | Don't care.      |

| 1    | 0        | 1         | 1   | Don't care.      |

| 0    | 1        | 1         | 1   | Don't care.      |

| 1    | 1        | 1         | 1   | Don't care.      |

#### **DAC Control Signal**

|     |     |     | DAC Output Voltage |     |     |     |     |                                             |

|-----|-----|-----|--------------------|-----|-----|-----|-----|---------------------------------------------|

| DB7 | DB6 | DB5 | DB4                | DB3 | DB2 | DB1 | DB0 | - DAC Output Voltage                        |

| 0   | 0   | 0   | 0                  | 0   | 0   | 0   | 0   | = V <sub>REF-</sub>                         |

| 0   | 0   | 0   | 0                  | 0   | 0   | 0   | 1   | = V <sub>LB</sub> + V <sub>REF-</sub>       |

| 0   | 0   | 0   | 0                  | 0   | 0   | 1   | 0   | = 2 × V <sub>LB</sub> + V <sub>REF-</sub>   |

| ~   | ~   | ~   | ~                  | ~   | ~   | ~   | ~   | ~                                           |

| 1   | 1   | 1   | 1                  | 1   | 1   | 1   | 0   | = 254 × V <sub>LB</sub> + V <sub>REF-</sub> |

| 1   | 1   | 1   | 1                  | 1   | 1   | 1   | 1   | = 255 × V <sub>LB</sub> + V <sub>REF-</sub> |

NOTE:  $V_{LB} = (V_{REF+} - V_{REF-})/256$ .

#### **DETAILED DESCRIPTION (continued)**

#### PWR\_DWN Register

| BIT        | DB7    | DB6    | DB5    | DB4    | DB3    | DB2    | DB1    | DB0    |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Definition | PD_AO8 | PD_AO7 | PD_AO6 | PD_AO5 | PD_AO4 | PD_AO3 | PD_AO2 | PD_AO1 |

| Default    | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

PWR\_DWN register is not readable. Setting the bit to 1 powers down the corresponding DAC channel. Clearing the bit brings it up. If all the channels are powered down then the bias circuit will be powered down as well.

#### **CONTROL** Register

| BIT        | DB7 | DB6 | DB5 | DB4 | DB3 | DB2    | DB1  | DB0     |

|------------|-----|-----|-----|-----|-----|--------|------|---------|

| Definition | N/A | N/A | N/A | N/A | RST | UPDATE | SYNC | 3K_PULL |

| Default    | Х   | Х   | Х   | Х   | Х   | 0      | 0    | 0       |

- RST = 1 Reset internal circuit other than the shift register. Will be automatically cleared to 0 after writing a 1. Since the reset doesn't hold, the next frame can be used for command. For example, at the first frame, the RST bit is written so that all DAC outputs reset to 0 at rising edge of the LD signal. The second frame can be a data writing command, but the DAC outputs won't be changed from 0 until writing of the data takes effect by the LD signal of the second frame.

- $3K_{PULL} = 1$  Enable the  $3k\Omega$  pull-down resistors for all the 8 channels. The pull-down resistors are only enabled in power-down mode.

- $3K_PULL = 0$  The pull-down resistance is around  $300k\Omega$ .

- SYNC = 1 The rising edge of LD signal only loads the data in shift register to DIN register indicated by ADDR but does not update the data register. LD will update all 8 channels when writing to channel 8.

- SYNC = 0 The rising edge of LD signal loads the data in shift register to DIN and DATA.

- UPDATE = 1 The rising edge of LD signal updates data in DIN register of all 8 channels to the corresponding data registers. The bit is then automatically cleared to 0.

Example one of a simultaneous update:

- 1. Write 0x02 to CONTROL register.

- 2. Write data to channel 1, to channel 2 ... to channel 7.

- 3. Writing data to channel 8 causes all the 8 channels to update at the same time. Then the following writings are still simultaneously updated.

- 4. Write 0x00 to CONTROL register to exit simultaneous update mode.

Example two of a simultaneous update:

- 1. Write 0x02 to CONTROL register.

- 2. Write data to channel 1, to channel 2 ... to channel 7.

- 3. Write 0x06 to CONTROL register to update all the 8 channels. Then the following writings are still simultaneously updated.

- 4. Write 0x00 to CONTROL register to exit simultaneous update mode.

## CHARACTERIZATION OF V<sub>AO</sub> - I<sub>AO</sub>

Figure 8. V<sub>AO</sub> - I<sub>AO</sub>

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (DECEMBER 2019) to REV.A  | Page |  |

|-------------------------------------------------|------|--|

| Changed from product preview to production data | All  |  |

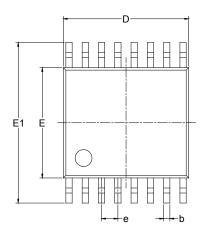

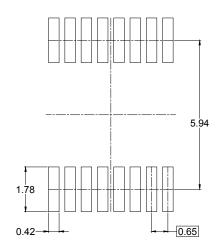

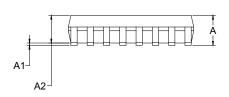

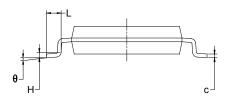

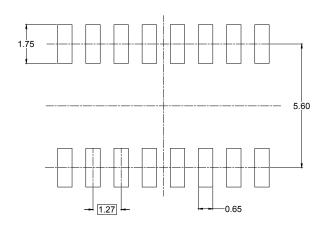

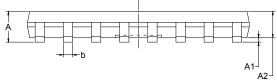

# PACKAGE OUTLINE DIMENSIONS TSSOP-16

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol  | -           | nsions<br>meters | Dimensions<br>In Inches |       |  |

|---------|-------------|------------------|-------------------------|-------|--|

| <b></b> | MIN         | MAX              | MIN                     | MAX   |  |

| А       |             | 1.200            |                         | 0.047 |  |

| A1      | 0.050       | 0.150            | 0.002                   | 0.006 |  |

| A2      | 0.800       | 1.050            | 0.031                   | 0.041 |  |

| b       | 0.190       | 0.300            | 0.007                   | 0.012 |  |

| С       | 0.090       | 0.200            | 0.004                   | 0.008 |  |

| D       |             | 5.100            | 0.191                   | 0.201 |  |

| Е       |             | 4.500 0.         | 0.169                   | 0.177 |  |

| E1      | 6.200 6.600 |                  | 0.244                   | 0.260 |  |

| е       | 0.650 BSC   |                  | 0.026 BSC               |       |  |

| L       | 0.500       | 0.700            | 0.02                    | 0.028 |  |

| Н       | 0.25 TYP    |                  | 0.01 TYP                |       |  |

| θ       | 1°          | 7°               | 1°                      | 7°    |  |

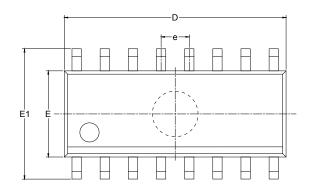

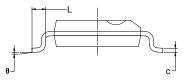

# PACKAGE OUTLINE DIMENSIONS SOIC-16

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions<br>In Millimeters |             | Dimensions<br>In Inches |       |  |

|--------|------------------------------|-------------|-------------------------|-------|--|

|        | MIN                          | MAX         | MIN                     | MAX   |  |

| Α      | 1.350                        | 1.350 1.750 |                         | 0.069 |  |

| A1     | 0.100                        | 0.250       | 0.004                   | 0.010 |  |

| A2     | 1.350                        | 1.550       | 0.053                   | 0.061 |  |

| b      | 0.330                        | 0.510       | 0.013<br>0.006          | 0.020 |  |

| С      | 0.170                        | 0.250       |                         | 0.010 |  |

| D      | 9.800                        | 10.200      | 0.386                   | 0.402 |  |

| E      | 3.800                        | 4.000       | 0.150                   | 0.157 |  |

| E1     | 5.800                        | 5.800 6.200 |                         | 0.244 |  |

| е      | 1.27                         | BSC         | 0.050                   | BSC   |  |

| L      | 0.400 1.270                  |             | 0.016                   | 0.050 |  |

| θ      | 0°                           | 8°          | 0°                      | 8°    |  |

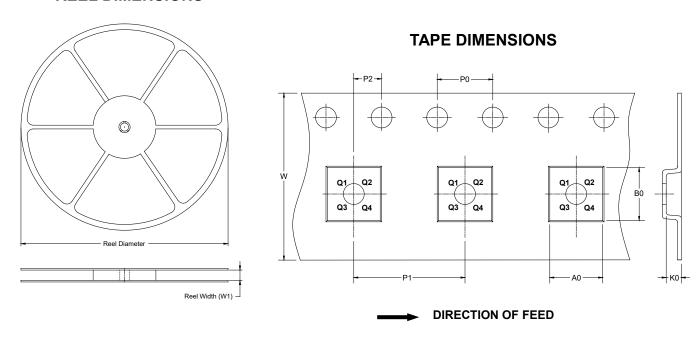

### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-16     | 13″              | 12.4                     | 6.90       | 5.60       | 1.20       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| SOIC-16      | 13"              | 16.4                     | 6.50       | 10.30      | 2.10       | 4.0        | 8.0        | 2.0        | 16.0      | Q1               |

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type Length (mm) |     | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------------------|-----|---------------|----------------|--------------|--------|

| 13"                   | 386 | 280           | 370            | 5            | 000002 |