## WUSB3801

## USB Type-C Configuration Channel Flippable Adapter

### Description

The WUSB3801 is a Type-C Configuration Channel (CC) Flippable Adapter chip with low power and high efficiency. The WUSB3801 supports channel identification of USB Type-C connector and auto detection of different power roles based on chip settings. This chip is compatible with USB Type-C Cable and Connector Specification Release 1.2 for varies of applications.

The WUSB3801 supports PIN control mode and I<sup>2</sup>C control mode through CTRL pin settings, and re-uses SDA (INOUT1)/SCL (INOUT2)/INTB (OUT3) pins to realize necessary functions in different control modes. ROLE pin is used for Source (SRC)/Sink (SNK)/Dual Role Power (DRP) mode selection of Type-C logic working state. The global enable signal comes from ENB pin with internal pull-up resistor for more feasibility.

## Applications

- Smart-phones

- Laptops

- Tablets

#### http//:www.willsemi.com

#### Features

- USB Type-C Cable and Connector

Specification Release 1.2 compatible

- Global power saving and active mode

- Pin or I<sup>2</sup>C controllable

- Support auto CC ports configuration

- Support SRC/SNK/DRP power mode

- Support DRP with Try.SNK or Try.SRC

- Support different current model controls and identifications (Default, 1.5A and 3.0A)

- Accurate internal CC termination resistance and current source with high precision

- High voltage EOS protection and DC 25V tolerance on CC1, CC2 and VBUSD pins

- Wide single power supply range: 2.7 ~ 5.5V

- QFN1616-12L packaging available (1.6x1.6x0.35mm)

#### **Order Information**

| Device          | Package     | Shipping       |  |

|-----------------|-------------|----------------|--|

| WUSB3801Q-12/TR | QFN1616-12L | 3000/Reel&Tape |  |

# **Revision History**

| Version | Date    | Owner   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0.0     | 2015-03 | Y. Shen | Initial draft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.1     | 2015-03 | Y. Shen | Support high voltage mode and ENB as global reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 0.2     | 2015-04 | Y. Shen | Type-C 1.1 compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 0.3     | 2015-08 | Y. Shen | Update $I_{host}$ from 110µA to 122.5µA. Update $I_{device}$ from 28µA to 22.5µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 0.4     | 2015-10 | Y. Shen | Support DRP with Try.SNK or Try.SRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0.5     | 2015-11 | Y. Shen | WUSB3801QB marking change from B* to G*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 0.6     | 2015-11 | Y. Shen | Add recommend land pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1.0     | 2016-05 | X. Chen | Type-C 1.2 compatible<br>Add general marking M<br>Use a clear function description for ID pin<br>Update high voltage DC from 20V to 25V<br>Update ESD HBM from 3500V to $\pm$ 4000V<br>Update ESD CDM from 1500V to $\pm$ 1500V<br>Update USB Max tri-state input threshold from V <sub>DD</sub> -0.5 to 2.9V<br>Update V <sub>H</sub> and V <sub>L</sub> for logic threshold voltage from 0.8*V <sub>DD</sub> to 1.05V<br>and from 0.2*V <sub>DD</sub> to 0.4V<br>Update V <sub>th_BUS</sub> from 0.78*V <sub>DD</sub> to 3.2V<br>Update I <sub>host</sub> max from 140µA to 160µA<br>Correct figures for threshold of Comparison and Status<br>Relationship<br>Update all state diagrams based on chip functions<br>Refine all descriptions and diagrams<br>Remove repetitious descriptions as those in USB Type-C<br>Specification |  |  |  |

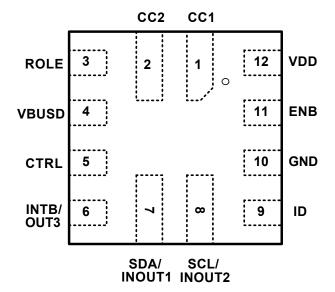

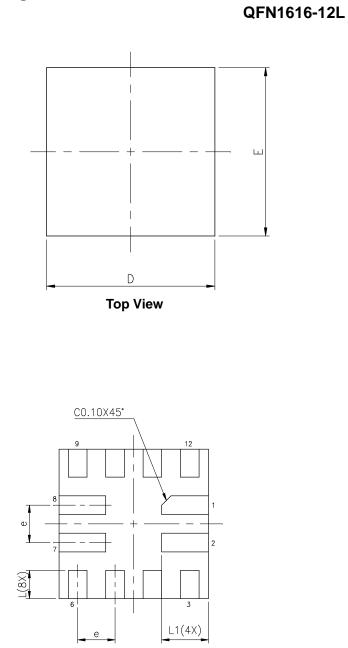

## Pin Configuration (Top View)

**Marking Information**

★ = Month Code (A~Z)

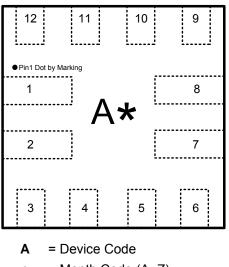

**Application Block Diagram**

# **Pin Descriptions**

| <b>D</b> ' |                |      |                                                                                                                                           |                                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin        | Name           | Туре | Function                                                                                                                                  | Comments                                                                                                                                                                              |  |  |  |  |  |  |  |

| 1          | CC1            | I/O  | Type-C CC logic channel signal<br>High voltage EOS protection                                                                             | Start from SNK when power on                                                                                                                                                          |  |  |  |  |  |  |  |

| 2          | CC2            | I/O  | Type-C CC logic channel signal<br>High voltage EOS protection                                                                             | Start from SNK when power on                                                                                                                                                          |  |  |  |  |  |  |  |

| 3          | ROLE           | AI   | Tri-state input control signal for working mode selection                                                                                 | Floating – DRP<br>VDD – SRC<br>GND – SNK                                                                                                                                              |  |  |  |  |  |  |  |

| 4          | VBUSD          | AI   | V <sub>BUS</sub> detection and high voltage<br>protection: DC 25V<br>AC lighting surge                                                    | Detect V <sub>BUS</sub> voltage                                                                                                                                                       |  |  |  |  |  |  |  |

| 5          | CTRL           | AI   | Tri-state input control signal for PIN or I <sup>2</sup> C control mode selection                                                         | Floating $-$ PIN control mode<br>VDD $-$ I <sup>2</sup> C control mode with<br>control address 7b'1101000<br>GND $-$ I <sup>2</sup> C control mode with<br>control address 7b'1100000 |  |  |  |  |  |  |  |

| 6          | INTB/          | DO   | Interruption output signal for I <sup>2</sup> C control mode                                                                              | INTB output Low active                                                                                                                                                                |  |  |  |  |  |  |  |

| 0          | OUT3           |      | OUT3:<br>Audio Acc. connection indification                                                                                               | H — No connection<br>L — Audio Acc. connected                                                                                                                                         |  |  |  |  |  |  |  |

| 7          | SDA/<br>INOUT1 | I/O  | I <sup>2</sup> C data input/output;<br>INOUT1 and INOUT2 combined to<br>identify the charging current mode<br>when a SRC/SNK is connected | INOUT2 and INOUT1 in PIN<br>control mode indifications<br>2b'11 – Default                                                                                                             |  |  |  |  |  |  |  |

| 8          | SCL/<br>INOUT2 | I/O  | I <sup>2</sup> C clock input;<br>INOUT1 and INOUT2 combined to<br>identify the charging current mode<br>when a SRC/SNK is connected       | 2b'10 — 1.5A<br>2b'00 — 3.0A<br>2b'01 — No connection                                                                                                                                 |  |  |  |  |  |  |  |

| 9          | ID             | AO   | Open drain output signal for SRC or<br>DRP operating as SRC                                                                               | Output Low when detects CC<br>channel is connected as SRC<br>or DRP operating as SRC                                                                                                  |  |  |  |  |  |  |  |

| 10         | GND            | G    | Global ground                                                                                                                             | —                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 11         | ENB            | AI   | Global enable signal                                                                                                                      | H — Power saving<br>L — Active                                                                                                                                                        |  |  |  |  |  |  |  |

| 12         | VDD            | Р    | Power                                                                                                                                     | 2.7 ~ 5.5V                                                                                                                                                                            |  |  |  |  |  |  |  |

# Table 1. Pin Descriptions

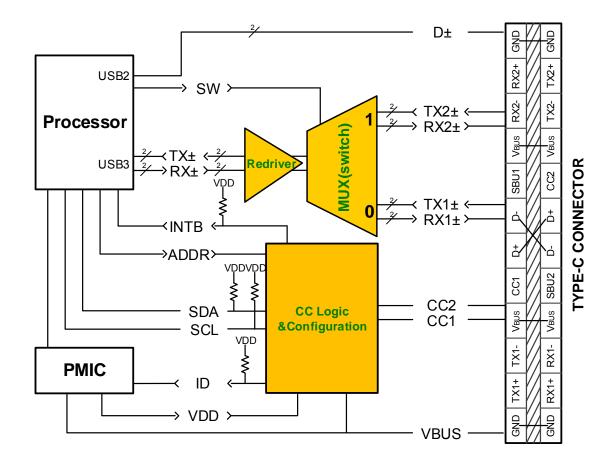

# **Block Diagram**

## Absolute Maximum Ratings

| Symbol            | Description                  | Range      | Unit |

|-------------------|------------------------------|------------|------|

| V <sub>BUSD</sub> | V <sub>BUS</sub> pin voltage | -0.3 ~ 25  | V    |

| V <sub>CCx</sub>  | CC pin voltage               | -0.3 ~ 25  | V    |

| V <sub>DD</sub>   | Power supply                 | -0.3 ~ 6.0 | V    |

| V <sub>IO</sub>   | Input IO voltage             | -0.3 ~ 3.6 | V    |

| T <sub>sto</sub>  | Storage temperature          | -65 ~ 150  | °C   |

| V <sub>HBM</sub>  | ESD HBM                      | ±4000      | V    |

| V <sub>CDM</sub>  | ESD CDM                      | ±1500      | V    |

#### Table 2. Absolute Maximum Ratings

The range is for stress ratings only. Stress exceeding the range specified in the Absolute Maximum Ratings may cause substantial damage to the device. Prolonged exposure to extreme conditions within the range may also affect device reliability.

# **Recommended Operation Conditions**

| Symbol                                     | Description                                           | Test Condition                                    | Min. | Тур. | Max. | Unit |

|--------------------------------------------|-------------------------------------------------------|---------------------------------------------------|------|------|------|------|

| V <sub>DD</sub>                            | Power supply                                          | -                                                 | 2.7  | -    | 5.5  | V    |

| $V_{\text{EN}_{L}}$                        | ENB pin Low voltage level                             | V <sub>DD</sub> =3.6V                             | -    | -    | 0.4  | V    |

| V <sub>EN_H</sub>                          | ENB pin High voltage level                            | V <sub>DD</sub> =3.6V                             | 1.15 | -    | -    | V    |

| V <sub>ID_L</sub> /<br>V <sub>INTB_L</sub> | ID/INTB pin Low voltage<br>level<br>Open drain output | V <sub>DD</sub> =3.6V<br>I <sub>Sink</sub> = -2mA | -    | -    | 0.4  | V    |

| $V_{\text{IO3_th}}$                        | USB tri-state input threshold                         | V <sub>DD</sub> =3.6V                             | 0.7  | -    | 2.9  | V    |

| Tj                                         | Junction temperature                                  | -                                                 | -40  | -    | 125  | °C   |

#### **Table 3. Recommended Operation Conditions**

# Electronics Characteristics (V<sub>DD</sub>=3.6V, T<sub>a</sub>=25°C, unless otherwise noted)

| Parameters                                      | Symbol                 | Test Conditions                                          | Min. | Тур.  | Max. | Unit |

|-------------------------------------------------|------------------------|----------------------------------------------------------|------|-------|------|------|

|                                                 |                        | ENB=Low<br>CC pins unattached                            | -    | 22.5  | 45   | μA   |

| Active current                                  | I <sub>DD_active</sub> | ENB=Low<br>In Attached.SRC state<br>Default current mode | -    | 122.5 | 160  | μA   |

| Power saving<br>current                         | I <sub>DD_disab</sub>  | ENB=High                                                 | -    | -     | 1    | μA   |

| Logic threshold                                 | V <sub>H</sub>         | V <sub>DD</sub> =3.6V                                    | 1.05 | -     | -    | V    |

| voltage                                         | VL                     | V <sub>DD</sub> =3.6V                                    | -    | -     | 0.4  | V    |

|                                                 | I <sub>H</sub>         | 3.0A mode setting                                        | 304  | 330   | 356  | μA   |

| Current source                                  | I <sub>M</sub>         | 1.5A mode setting                                        | 166  | 180   | 194  | μA   |

|                                                 | ID                     | Default mode setting                                     | 64   | 80    | 96   | μA   |

| Resistor load                                   | Rd                     | -                                                        | 4.6  | 5.1   | 5.6  | kΩ   |

| Compositor                                      | V <sub>th_H</sub>      | 3.0A mode setting                                        | 1.16 | 1.23  | 1.31 | V    |

| Comparator                                      | V <sub>th_M</sub>      | 1.5A mode setting                                        | 0.61 | 0.66  | 0.70 | V    |

| threshold voltage                               | V <sub>th_D</sub>      | Default mode setting                                     | 0.15 | 0.2   | 0.25 | V    |

| V <sub>BUS</sub> detection<br>threshold voltage | V <sub>th_BUS</sub>    | V <sub>DD</sub> =3.6V                                    | 2.9  | 3.2   | 3.5  | V    |

**Table 4. Electrical Characteristics**

## **Function Descriptions**

#### **General Description**

The WUSB3801 is a Type-C Configuration Channel Flippable Adapter chip with low power and high efficiency. The WUSB3801 supports channel identification of USB Type-C connector and auto detection of different power roles based on chip settings. It has high voltage protection circuits on CC1/CC2/VBUSD pins and supports both DC up to 25V and AC lighting surge. This chip is compatible with USB Type-C Cable and Connector Specification Release 1.2 for varies of applications.

#### **Logic Control Block**

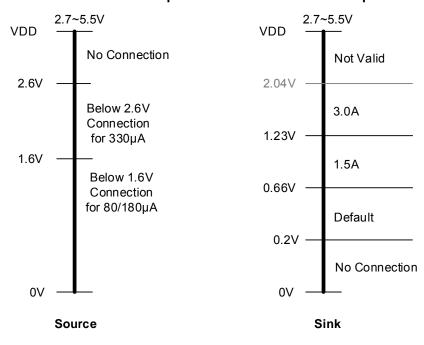

The logic control block receives the outer control signals, detects CC connection status using voltage level comparisons of CC pins for different connection topologies and settings, and outputs the detected information of communication path. Comparison results showing CC signals voltage range are sent to logic control block for state machine and then the connection status of related working mode will be identified. When connection status changes, the logic control block will update outputs of pins and registers. The figures as below show the boundaries of status.

Threshold of Comparison and Status Relationship

#### Work Mode Feature

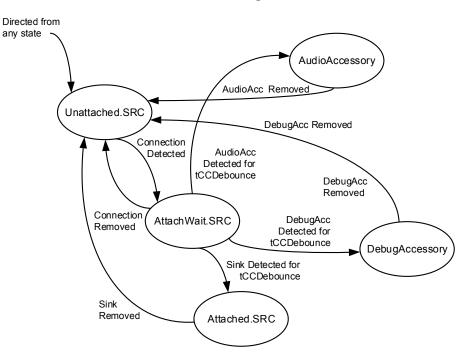

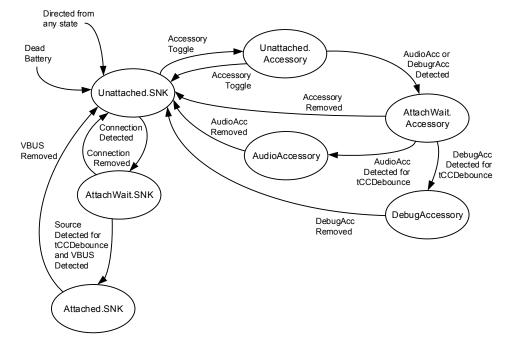

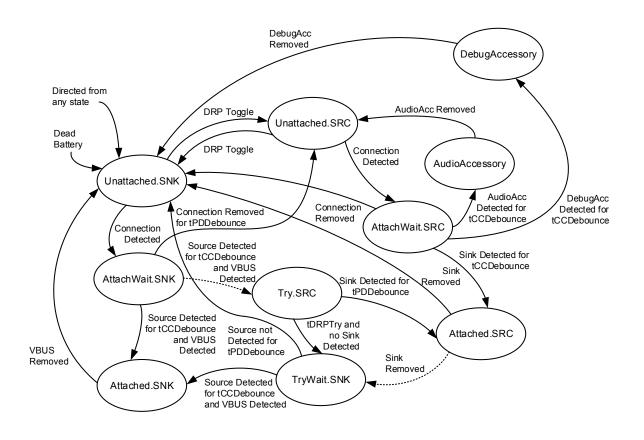

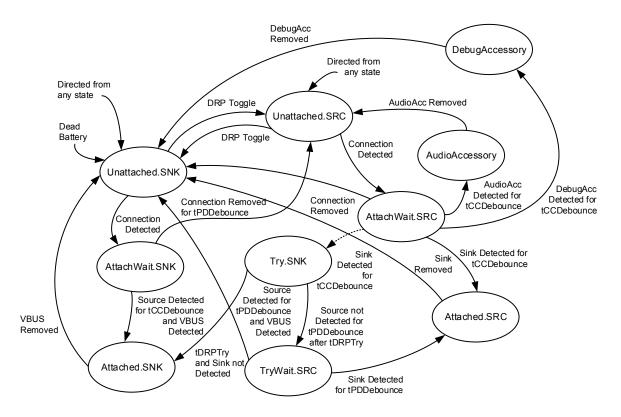

According to CC connection status and detection results, the chip can work as SRC (Host), SNK (Device) or DRP mode which are shown in the following figures.

**SRC State Diagram**

SNK with Accessory Support State Diagram

DRP with Accessory and Try.SRC Support State Diagram

DRP with Accessory and Try.SNK Support State Diagram

#### **Communication Interfaces**

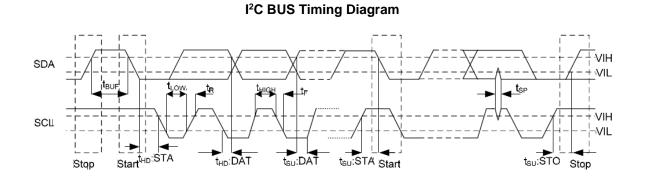

#### I<sup>2</sup>C Interface

The chip can take communications over I<sup>2</sup>C bus which supports up to 400 kHz clock when CTRL pin is not floating (connected to VDD or GND). Two setting values would result in different I<sup>2</sup>C device addresses as shown in Table 7.

|           | Pin Setting | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 |

|-----------|-------------|------|------|------|------|------|------|------|

| Address 1 | VDD         | 1    | 1    | 0    | 1    | 0    | 0    | 0    |

| Address 2 | GND         | 1    | 1    | 0    | 0    | 0    | 0    | 0    |

#### Table 7. Address Table Controlled by CTRL Pin

## I<sup>2</sup>C Bus Timing

### Electrical Characteristics of I<sup>2</sup>C

| Symbol              | Parameter                                                                        | Test<br>Conditions | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------------------------------|--------------------|------|------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                                              | -                  | -    | -    | 400  | kHz  |

| V <sub>DD_I2C</sub> | Power supply range for I <sup>2</sup> C                                          | -                  | 1.65 | -    | 3.6  | V    |

| VIH                 | Logic high level voltage (Note 1)                                                | -                  | 1.2  | -    |      | V    |

| VIL                 | Logic low level voltage (Note 1)                                                 | -                  | -    | -    | 0.4  | V    |

| l <sub>sink</sub>   | Sink current at low level (open drain) (Note 1)                                  | -                  | -    | 1.6  | -    | mA   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                 | -                  | 1.3  | -    | -    | μs   |

| thd_sta             | Hold time START condition. After this period, the first clock pulse is generated | -                  | 0.6  | -    | -    | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                      | -                  | 1.3  | -    | -    | μs   |

| <b>t</b> HIGH       | HIGH period of the SCL clock                                                     | -                  | 0.6  | -    | -    | μs   |

| t <sub>su_sta</sub> | Set-up time for a repeated START condition                                       | -                  | 0.6  | -    | -    | μs   |

| t <sub>HD_DAT</sub> | Data hold time between SDA and SCL falling edge                                  | -                  | 0    | -    | -    | μs   |

| t <sub>su_dat</sub> | Data set-up time                                                                 | -                  | 100  | -    | -    | ns   |

| tr                  | Rise time for SDA and SCL signals (Note 2)                                       | -                  | -    | -    | 300  | ns   |

| t <sub>f</sub>      | Fall time for SDA and SCL signals (Note 2)                                       | -                  | -    | -    | 300  | ns   |

| t <sub>su_sto</sub> | Set-up time for STOP condition                                                   | -                  | 0.6  | -    | -    | μs   |

| <b>–</b>            | Width of deglitch at input termination                                           | SCL                | -    | 200  | -    | ns   |

| T <sub>deg</sub>    | Width of deglitch at input termination                                           | SDA                | -    | 250  | -    | ns   |

| Cb                  | Capacitive load for each bus line                                                | -                  | -    | -    | 400  | pF   |

Table 8. Electrical Characteristics of I<sup>2</sup>C

Note 1: Guaranteed by design

Note 2: tr and tf are timing from 0.3\*VDD to 0.7\*VDD

## I<sup>2</sup>C Register Map

| Addr. | Register     | Туре         | Bit7                                                                      | Bit6                                               | Bit5    | Bit4                                   | Bit3                          | Bit2                                                                                         | Bit1            | Bit0                                                                                 |  |                                                                                       |  |

|-------|--------------|--------------|---------------------------------------------------------------------------|----------------------------------------------------|---------|----------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------|--|

| 01H   | Device ID    | R            |                                                                           | Version                                            | ID: 000 | 10                                     |                               | V                                                                                            | Vendor ID: 110  |                                                                                      |  |                                                                                       |  |

|       |              |              | Acc.<br>Support                                                           | Wor                                                |         | ,                                      |                               | Work I                                                                                       | Node            | Interruption<br>Control                                                              |  |                                                                                       |  |

| 02H   | Control      | R/W          | 0: Yes<br>1: No                                                           | 10 <sup>.</sup> Try SRC 01 <sup>.</sup> 1 5A       |         | 5A                                     | 00: SNK<br>01: SRC<br>10: DRP |                                                                                              | 1               |                                                                                      |  |                                                                                       |  |

| 03H   | Interruption | R /<br>Clear |                                                                           | Reserved                                           |         |                                        |                               |                                                                                              | 00: N<br>01: At | ach/Attach<br>o Interruption<br>tached<br>etached                                    |  |                                                                                       |  |

|       |              |              | V <sub>BUS</sub><br>Detection<br>as SNK                                   | Detection Current Plugged Port Status              |         |                                        |                               | t Status                                                                                     | Plug            | Orientation                                                                          |  |                                                                                       |  |

| 04H   | CC Status    | R            | 0: V <sub>BUS</sub><br>not<br>detected<br>1: V <sub>BUS</sub><br>detected | 00: Standby<br>01: Default<br>10: 1.5A<br>11: 3.0A |         | 00: Standby<br>01: Default<br>10: 1.5A |                               | not<br>detected<br>1: V <sub>BUS</sub><br>00: Standby<br>01: Default<br>10: 1.5A<br>11: 3.0A |                 | 000: Standby<br>001: SNK<br>010: SRC<br>011: Audio Accessory<br>100: Debug Accessory |  | 00: Standby<br>01: CC1 connected<br>10: CC2 connected<br>11: CC1 and CC2<br>connected |  |

Table 9. I<sup>2</sup>C Register Map

## **Function Description**

Registers are used for read/write settings in I2C control mode.

Status of USB Type-C connector is detected and updated in register map automatically by internal state machine. When any update occurs in register map after the last I2C reads, the chip would keep the interruption pin (INTB) at low level. Otherwise, the chip would cancel the interruption signal (INTB=1).

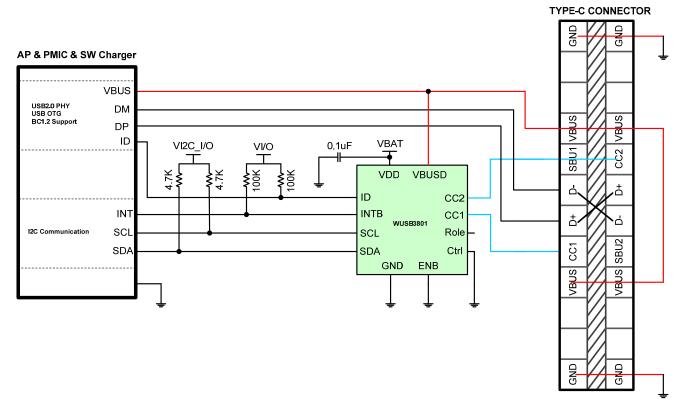

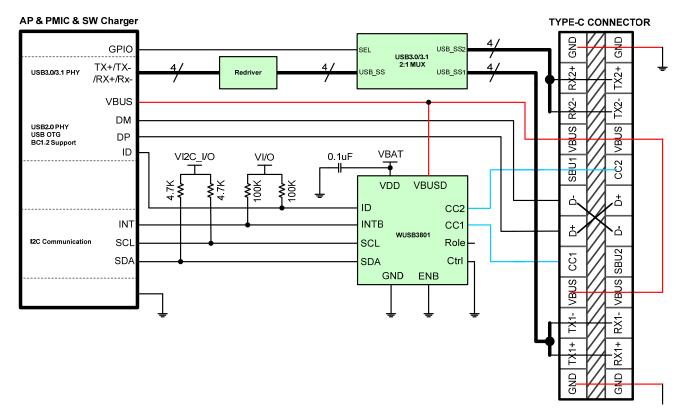

# **Typical Application Schematics**

## DRP Mode for I<sup>2</sup>C Control with USB2.0

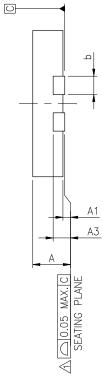

# Package Outline Dimensions

**Bottom View**

Side View

| Symbol | Dimensions in millimeter |           |      |  |  |  |  |

|--------|--------------------------|-----------|------|--|--|--|--|

| Symbol | MIN.                     | NOM.      | MAX. |  |  |  |  |

| A      | 0.30                     | 0.35      | 0.40 |  |  |  |  |

| A1     | 0.00                     | 0.00 0.02 |      |  |  |  |  |

| A3     | 0.127 Ref.               |           |      |  |  |  |  |

| b      | 0.15                     | 0.20      | 0.25 |  |  |  |  |

| D      | 1.55                     | 1.60      | 1.65 |  |  |  |  |

| E      | 1.55                     | 1.60      | 1.65 |  |  |  |  |

| е      |                          | 0.40 BSC. |      |  |  |  |  |

| L      | 0.25                     | 0.30      | 0.35 |  |  |  |  |

| L1     | 0.45                     | 0.50      | 0.55 |  |  |  |  |

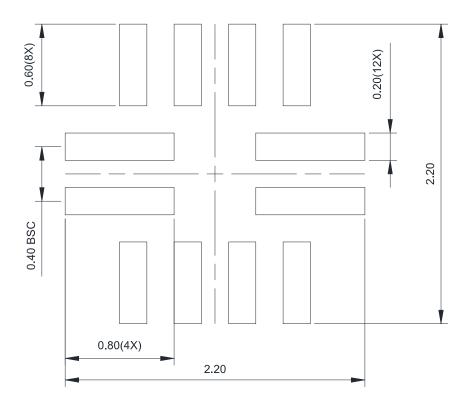

# **Recommend Land Pattern**

# RECOMMENDED LAND PATTERN

All dimensions are in millimeters