TPS65651

#### SLVSD67-SEPTEMBER 2015

# **TPS65651 Triple-Output AMOLED Display Power Supply**

#### 1 Features

- 2.9-V to 4.5-V Input Voltage Range

- Synchronous Boost Converter (AVDD)

- 5.8-V to 7.9-V Output Voltage (programmable)

- 6.1-V Default Output Voltage

- 1% Accuracy

- 80-mA Output Current Capability

- 100-mA Output Current Protection (±20%)

- V<sub>I</sub> to V<sub>O</sub> and V<sub>O</sub> to V<sub>I</sub> Isolation

- Synchronous Boost Converter (ELVDD)

- 4.6-V to 5-V Output Voltage (programmable)

- 4.6-V Default Output Voltage

- 0.5% Accuracy

- 300-mA Output Current Capability

- External Output Voltage Sensing Pin for Load Drop Compensation

- Excellent Line Transient Response

- V<sub>I</sub> to V<sub>O</sub> and V<sub>O</sub> to V<sub>I</sub> Isolation

- Synchronous Inverting Buck-Boost Converter (ELVSS)

- -5.4-V to -1.4-V Output Voltage (programmable)

- -2.5-V Default Output Voltage

- 1.2% Accuracy at -2.5 V (±30 mV)

- 300-mA Output Current Capability

- V<sub>I</sub> to V<sub>O</sub> and V<sub>O</sub> to V<sub>I</sub> Isolation

- Single-Wire Digital Interface for Programming

- Short Circuit Protection

- Thermal Shutdown

- Available in 3-mm × 3-mm x 0.75-mm 16-Pin WQFN Package

## 2 Applications

- Smartphones

- Small Size Tablets

- Active Matrix OLED Displays ≤ 8"

## 3 Description

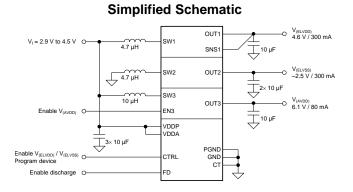

The TPS65651 is designed to drive AMOLED displays (Active Matrix Organic Light Emitting Diode) requiring V<sub>(AVDD)</sub>, V<sub>(ELVDD)</sub> and V<sub>(ELVSS)</sub>. The device integrates a boost converter for V<sub>(ELVDD)</sub>, an inverting buck-boost converter for V<sub>(ELVSS)</sub> and a boost converter for V<sub>(AVDD)</sub>, which are suitable for battery operated products. The digital interface control pin (CTRL) allows programming V<sub>(AVDD)</sub>, V<sub>(ELVDD)</sub>, V<sub>(ELVDD)</sub> and V<sub>(ELVSS)</sub> in digital steps. The TPS65651 uses a novel technology enabling excellent line and load regulation.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| TPS65651    | WQFN (16) | 3.00 mm x 3.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# 4 Revision History

| DATE           | DATE | NOTES            |

|----------------|------|------------------|

| September 2015 | *    | Initial release. |

## To request a full data sheet, please send an email to:

display\_contact@list.ti.com

### 5 Device and Documentation Support

#### 5.1 Device Support

#### 5.2 Documentation Support

#### 5.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 5.4 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 5.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 5.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 6 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

# PACKAGE OPTION ADDENDUM

18-Sep-2015

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TPS65651RTER     | ACTIVE | WQFN         | RTE     | 16   | 3000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | T65651         | Samples |

| TPS65651RTET     | ACTIVE | WQFN         | RTE     | 16   | 250     | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | T65651         | Samples |

# RTE (S-PWQFN-N16) PLASTIC QUAD FLATPACK NO-LEAD

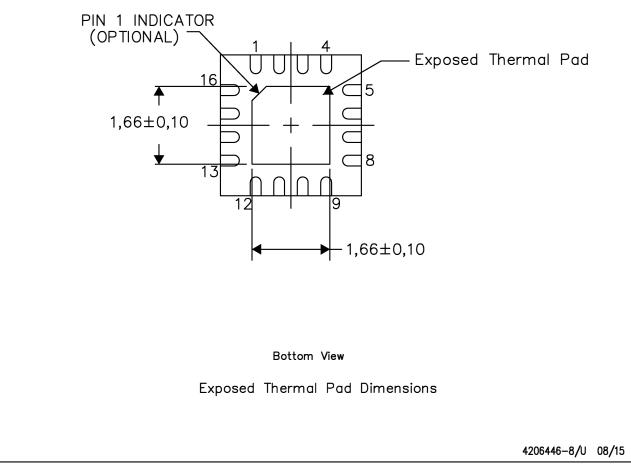

#### THERMAL INFORMATION

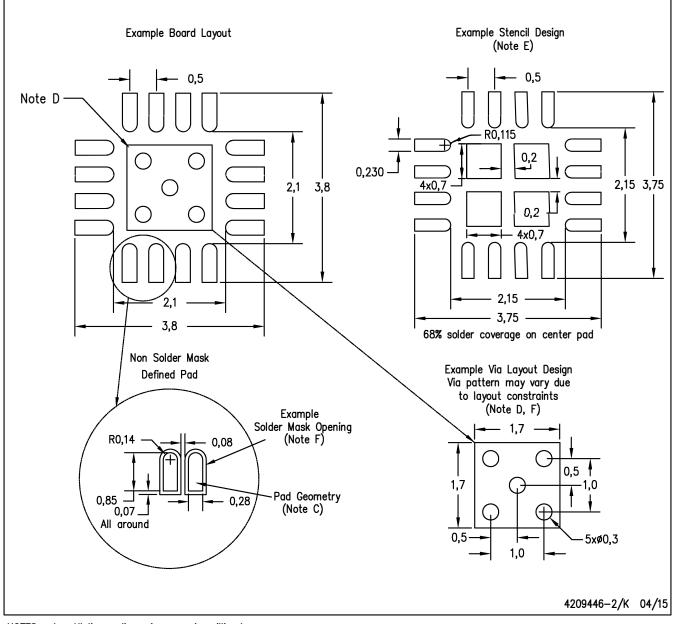

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

# RTE (S-PWQFN-N16) PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.