# SGM2541 28V/16V Bidirectional Load Switch with Wireless/Dual Input Capability

## GENERAL DESCRIPTION

The SGM2541 is a high-current, low-loss bidirectional load switch and over-voltage protection (OVP) device with wireless/dual input capability.

The device supports up to 20VDC operating input voltage (28VDC withstand) at USBIN pins, and a 16VDC reverse voltage blocking feature at OUT pins. The SGM2541 provides input voltage-clamped protection for input surge events up to 120V. The integrated high-speed input over-voltage protection capability ensures safe operation for surge events that occur during the ON-state (conducting) or OFF-state (non-conducting). The two OVP threshold voltages (17V/13V) can be programmed through VP pin.

A second input and 2:1 power multiplexer can be achieved by connecting a compatible wireless receiver (wireless Rx) output to the load switch OUT pins.

The bidirectional device can detect and support USB-OTG applications. It also includes under-voltage lockout, over-voltage lockout and over-temperature protection circuits designed to automatically isolate the power switch terminals when a fault condition occurs.

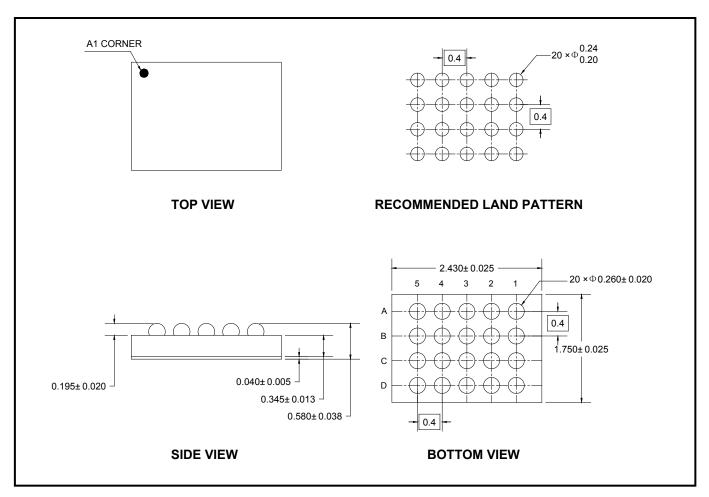

The SGM2541 is available in the Green WLCSP-2.43× 1.75-20B package. It operates over an ambient temperature range of -40°C to +85°C.

## **FEATURES**

- Bidirectional Switch for USBIN and OUT to Allow On-The-Go (OTG) Mode

- Input Voltage Range:

3V to 20V at USBIN and 3V to 16V at OUT

- Programmable OVP Threshold Voltages

- 28V Tolerance on USBIN Pin

- 120V Surge Protection

- 5A Continuous Current from USBIN to OUT

- 5A Continuous Current from OUT to USBIN in OTG Mode

- Low On-Resistance: 28mΩ (TYP)

- 1.4V Control Logic

- Soft-Start to Reduce Input Peak Current

- Available in Green WLCSP-2.43×1.75-20B Package

- -40°C to +85°C Operating Temperature Range

## **APPLICATIONS**

**Smart Phone**

Tablet PC

Mobile Devices with Wireless Charging Options

## PACKAGE/ORDERING INFORMATION

| MODEL |         | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |  |

|-------|---------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|--|

|       | SGM2541 | WLCSP-2.43×1.75-20B    | -40°C to +85°C                    | SGM2541YG/TR       | XXXXX<br>2541YG    | Tape and Reel, 3000 |  |

NOTE: XXXXX = Date Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Vusbin_absmax                                                         | 28V            |

|-----------------------------------------------------------------------|----------------|

| $V_{\text{USBIN}}$ to $V_{\text{OUT}}$ (Differential Input, Blocking) | 28V            |

| $V_{\text{OUT}}$ to $V_{\text{USBIN}}$ (Differential Input, Blocking) | 16V            |

| Vout_max, Vusb_sns                                                    | 20V            |

| Control Pin Voltages                                                  | 6V             |

| Junction Temperature                                                  | +150°C         |

| Storage Temperature Range                                             | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)                                     | +260°C         |

#### RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range         | 3V to 20V     |

|-----------------------------|---------------|

| Operating Temperature Range | 40°C to +85°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time.

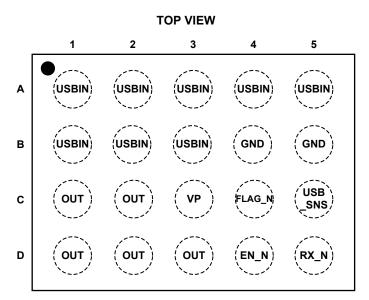

# **PIN CONFIGURATION**

WLCSP-2.43×1.75-20B

# **PIN DESCRIPTION**

| PIN                 | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 - A5,<br>B1 - B3 | USBIN   | Power Pin, Load Switch Input Pin. Connect a capacitor from this pin to the GND plane.                                                                                                                                                                                                                                                                                                            |

| B4, B5              | GND     | Ground Pin. Connect this pin to the external ground plane close to the USBIN decoupling capacitors.                                                                                                                                                                                                                                                                                              |

| C1, C2,<br>D1 - D3  | OUT     | Power Pin, Load Switch Output Pin. Connect this pin to the output capacitors, charger input pin, and wireless Rx output node for dual input configurations.                                                                                                                                                                                                                                      |

| C3                  | VP      | Digital Input. OVP voltage programming pin allows programming of one of two OVP-fast voltage thresholds. Connect the pin to GND to select 17V (TYP). Float the pin to select 13V (TYP).                                                                                                                                                                                                          |

| C4                  | FLAG_N  | Digital I/O Pin. The flag pin is pulled High to indicate to the system when OTG mode can be triggered in autonomous mode. Slave mode: Pull this pin logic Low, or tie to external GND plane. Autonomous mode: Connect to the system digital input/output pin (or equivalent) that pulls logic Low to enter OTG mode when USBIN is connected to an OTG load and a power source is applied to OUT. |

| C5                  | USB_SNS | Analog Output Pin. USB_SNS is a Clamped USBIN Sense Pin. In slave mode, connect this pin to the system's input sense pin that can respond to a valid USBIN voltage. This pin is optional in autonomous mode for system diagnostic purposes. An optional ceramic capacitor may be added from this pin to GND, sized as needed.                                                                    |

| D4                  | EN_N    | Digital Input Pin. Active Low Logic Enable Pin. Slave mode: Connect this pin to the system's enable logic pin. Autonomous mode: Pull this pin logic Low, or tie it to the external GND plane.                                                                                                                                                                                                    |

| D5                  | RX_N    | Digital I/O Pin. Wireless Rx Active Low Logic Enable Pin. Slave mode: Pull this pin logic Low, or tie to an external GND plane. Autonomous mode: Connect this pin to the wireless Rx active Low enable pin if a system output control pin is not available.                                                                                                                                      |

# **ELECTRICAL CHARACTERISTICS**

$(V_{USBIN} = 5V, V_{OUT} = 5V, T_A = -40^{\circ}C$  to +85°C, typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                               | SYMBOL                              | CONDITIONS                                                                                                                                        | MIN | TYP          | MAX              | UNITS |

|---------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|------------------|-------|

| Input Voltage Range                                     | V <sub>USBIN</sub>                  |                                                                                                                                                   | 3   |              | 20               | V     |

| Output Voltage Range                                    | V <sub>OUT</sub>                    |                                                                                                                                                   | 3   |              | V <sub>OVP</sub> | V     |

| Input/Output Under-Voltage Lockout                      | $V_{UVLO}$                          |                                                                                                                                                   |     | 2.8          |                  | V     |

| UVLO Hysteresis                                         | V <sub>UVLO_HYS</sub>               |                                                                                                                                                   |     | 0.5          |                  | V     |

| Input Over-Voltage Protection Threshold                 | $V_{OVP}$                           | $V_{\text{USBIN}}$ > $V_{\text{OVP}}$ enters fault mode; the VP pin is tied to ground.                                                            |     | 17           |                  | V     |

| input 676. Voltage Frotosalon Fillochola                | ▼ OVP                               | $V_{\text{USBIN}} > V_{\text{OVP}}$ enters fault mode; the VP pin is floating.                                                                    |     | 13           |                  | V     |

| V <sub>OVP</sub> Hysteresis                             | $V_{OVP\_HYS}$                      |                                                                                                                                                   |     | 0.3          |                  | V     |

| Maximum USB_SNS Pin Clamping Voltage                    | $V_{USB\_SNS}$                      | $I_{USB\_SNS}$ = 0, the VP pin is tied to ground.<br>$I_{USB\_SNS}$ = 0, the VP pin is floating.                                                  |     | 18.5<br>14.8 |                  | V     |

| Sense Pin Voltage Drop When Loaded                      | $\Delta V_{USB\_SNS}$               | $I_{USB\_SNS} = 20$ mA                                                                                                                            |     | 20           |                  | mV    |

| Input Quiescent Current in Operating State              |                                     | USBIN-GND current (operating state).                                                                                                              |     | 135          |                  | μA    |

| Input Quiescent Current in Operating State              | I <sub>Q_USBIN_OP</sub>             | USBIN-GND current (clamping).                                                                                                                     |     | 133          | 5                | mA    |

| , ,                                                     | IQ_USBIN_CLAMP                      | Standby state, FLAG_N = high and/or                                                                                                               |     |              |                  |       |

| OUT Float Voltage                                       | V <sub>USBIN-OUT(FLOAT)</sub>       | $EN_N = high; V_{USBIN} = 4.5V to 16V.$                                                                                                           |     |              | 2                | V     |

| USBIN Float Voltage                                     | $V_{\text{OUT-USBIN(FLOAT)}}$       | OTG state, EN_N = low; V <sub>USBIN</sub> = 4.5V to V <sub>USBIN_MAX</sub> .                                                                      |     |              | 2                | V     |

| ON Resistance                                           | Ron                                 | R <sub>DS(ON)</sub> measured between USBIN and                                                                                                    |     | 28           |                  | mΩ    |

|                                                         | TON                                 | OUT, T <sub>AMB</sub> = +25°C, EN_N = low.                                                                                                        |     |              |                  | 11132 |

| Continuous Output Current                               | I <sub>OUT</sub> , I <sub>OTG</sub> |                                                                                                                                                   |     | ±5.0         |                  | Α     |

| OUT Discharge Resistance                                | R <sub>DIS_OUT</sub>                | Measured from the OUT to GND during the discharge event.                                                                                          |     | 500          |                  | Ω     |

| Input Debounce Time                                     | $t_{DG}$                            | V <sub>UVLO</sub> < V <sub>USBIN</sub> < V <sub>OVPFAST</sub> , soft-start starts after the debounce time (rising UVLO, falling OVP); EN_N = low. |     | 50           |                  | ms    |

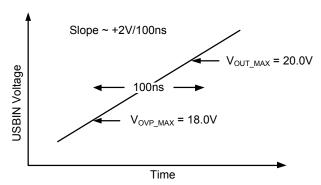

| Input Rising Disable Delay                              | t <sub>OVP-DLY</sub>                | Valid V <sub>USBIN</sub> which transitions to V <sub>USBIN</sub> > OVP fast event.                                                                |     | 100          | 200              | ns    |

| Logic Pin Turn-On Enable Delay: EN_N, FLAG_N            | t <sub>LDELAY</sub>                 | Time delay from EN_N/FLAG_N enable/<br>disable load switch, excluding a soft-<br>start.                                                           |     |              | 200              | μs    |

| Input Capacitance                                       | C <sub>USBIN</sub>                  | Actual capacitance.                                                                                                                               |     | 10           |                  | μF    |

| OTG Hot Swap Capacitance                                | C <sub>OTG</sub>                    | Actual capacitance.                                                                                                                               |     |              | 200              | μF    |

| Output Capacitance                                      | Соит                                | Actual capacitance.                                                                                                                               |     | 20           |                  | μF    |

| Input Leakage Current: EN_N, FLAG_N                     | I <sub>LEAK</sub>                   | $V_{USBIN}/V_{OUT} = 5V.$                                                                                                                         |     |              | 1                | μA    |

| Shutdown Supply Current                                 | I <sub>SHDN</sub>                   | EN_N = high, V <sub>USBIN</sub> /V <sub>OUT</sub> = 5V                                                                                            |     | 120          |                  | μA    |

| ENABLE, START-UP, CLAMP FEATURES                        |                                     |                                                                                                                                                   |     | •            |                  |       |

| Logic Input Threshold High Level                        | V <sub>IH</sub>                     |                                                                                                                                                   | 1.4 |              |                  | V     |

| Logic Input Threshold Low Level                         | V <sub>IL</sub>                     |                                                                                                                                                   |     |              | 0.4              | V     |

| Logic Output Threshold High Level                       | V <sub>OH</sub>                     |                                                                                                                                                   | 1.6 |              |                  | V     |

| Logic Output Threshold Low Level                        | V <sub>OL</sub>                     |                                                                                                                                                   |     |              | 0.6              | V     |

| Open Drain Internal Pull-Up Resistance: FLAG_N and RX_N | R <sub>PULL-UP</sub>                |                                                                                                                                                   |     | 500          |                  | kΩ    |

| Soft-Start Time                                         | t <sub>s-start</sub>                | Bidirectional. USBIN to OUT or OUT to USBIN (OTG modes).                                                                                          |     | 0.8          | 1.0              | ms    |

| Maximum Input Voltage Clamp During Surge Event          | V <sub>USBCLAMP</sub>               | Conditions = IEC 61000-4-5, $1.2/50\mu s$ , $R_S = 2\Omega$ .                                                                                     |     |              | 120              | V     |

| THERMAL                                                 |                                     |                                                                                                                                                   |     |              |                  |       |

| Over-Temperature Shutdown Threshold                     | t <sub>SD</sub>                     | Temperature Rising.                                                                                                                               |     | 150          |                  | °C    |

| Over-Temperature Shutdown Hysteresis                    | $t_{HYS}$                           |                                                                                                                                                   |     | 15           |                  | °C    |

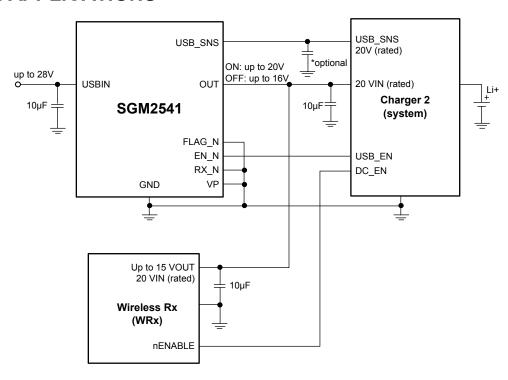

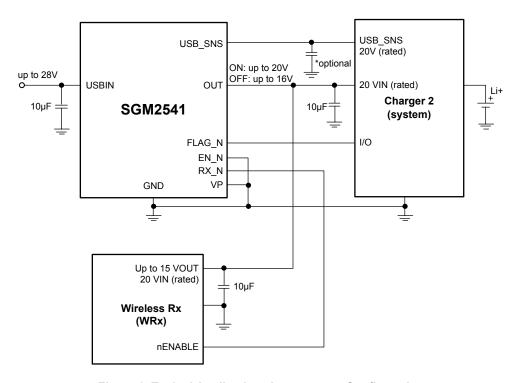

# TYPICAL APPLICATIONS

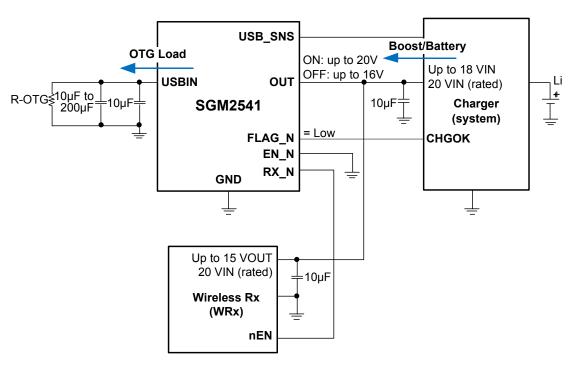

Figure 1. Typical Application, Slave Configuration

Figure 2. Typical Application, Autonomous Configuration

# Clamp USB\_SNS Ctl 28V 16V USBIN [ OUT < 5V Į Š 28V 17V FLAG N (nom) 2×500kΩ Control EN\_N RX N

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Block Diagram

**GND**

## **OPERATION**

The SGM2541 bidirectional load switch is designed for systems or chargers with high voltage quick charge capability and as well as wireless charging capabilities. The addition of a wireless Rx with an enable/disable pin allows the load switch to implement an equivalent 2:1 power multiplexer (PMUX) as shown in Figure 1. When disabled, the wireless Rx withstand voltage must be greater than or equal to 20V, the load switch's maximum output operating voltage.

The load switch can transition between the OFF-state/ standby-state and ON-state/OTG modes, based on the input devices powered states (USBIN adapter and/or wireless Rx) and logic I/O pins.

## **PMUX Operating Modes**

The 2:1 PMUX can operate in slave or autonomous modes. Slave mode allows the charger (system) to act as a master and determine the input priority, while autonomous mode assigns the input priority to the USBIN power source over the wireless Rx.

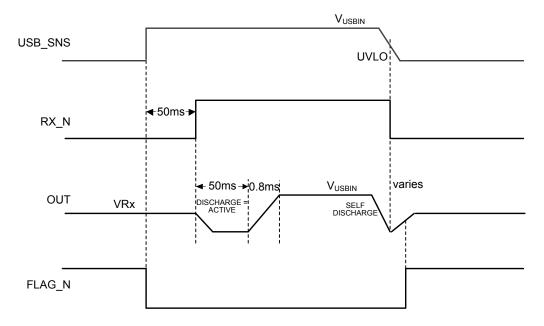

Both slave and autonomous modes include a 50ms input debounce delay and 0.8ms in rush periods. Autonomous mode includes a 50ms automatic

break-before-make plus discharge period that is disabled in slave mode by grounding the RX\_N pin.

#### **Slave Mode**

In slave mode, the charger (system) acts as the master, disables the wireless Rx, and activates the load switch ON-state via the EN\_N pin. The slave mode allows the system (charger) to assign the priority of the input power source when both power sources are active.

In slave mode, toggling EN\_N pin triggers the standby-state, ON-state, or ON-state/OTG modes. In OTG slave mode, a low input voltage threshold is detected at the USB\_SNS pin. Toggling EN\_N pin to Low triggers OTG mode, the wireless Rx may be enabled by the charger (system) as follows: the system (charger) that controls OTG concurrent mode requires that the master enable the boost and/or wireless Rx. OTG mode is triggered when the master detects that the necessary conditions are met.

NOTE: Both the FLAG\_N and the RX\_N pins are tied to GND in slave mode. OTG concurrent mode requires slave mode.

#### **Autonomous Mode**

In autonomous mode, the load switch controls input/wireless priority. The load switch controller disables the wireless Rx and activates the load switch ON-state after a fixed time delay when a valid USB\_SNS voltage is detected. Autonomous mode gives priority to the USBIN input.

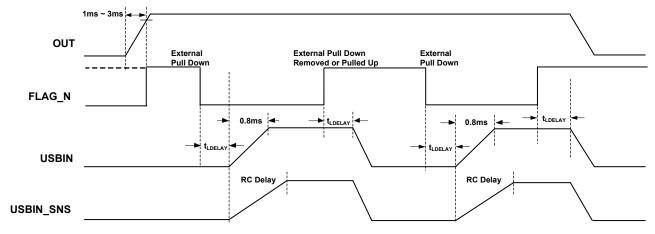

The system interfaces with valid USBIN or OUT, when a low input voltage threshold is detected at USBIN pin, it enters the OTG autonomous mode. Toggling FLAG\_N pin to Low triggers OTG mode since EN\_N pin is tied to ground, after RX\_N pin is tied to High disables the wireless Rx. See Figure 4 below.

NOTE: The EN\_N pin is tied to ground in autonomous mode.

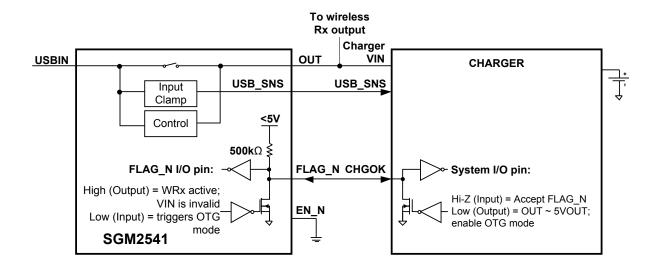

#### FLAG\_N Logic in Autonomous Mode

The FLAG\_N pin is a bidirectional input/output pin that controls the transition to and from OTG modes while in autonomous mode.

When USBIN pin is disconnected (floating) and a valid OUT voltage is detected, the FLAG\_N pin serves as an output signal and FLAG\_N = logic High. Subsequently, the load switch can be activated by toggling the FLAG\_N = logic Low, which triggers the OTG mode by transitioning into the ON-state.

- After FLAG\_N = logic Low, OTG mode is triggered after t<sub>LDELAY</sub> debounce delay, plus a 0.8ms soft-start time

- Ignore FLAG\_N = logic Low if the load switch is in the fault/OVP states.

| USB_SNS                                                                                                                                                                            | OUT   | FLAG_N | СНСОК | LOAD SWITCH BEHAVIOR (EN_N = HIGH)                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-----------------------------------------------------------------------------------------------------------|

| <uvlo< td=""><td>&gt;UVLO</td><td>High</td><td>Hi-Z</td><td>Load switch = OFF, and OTG mode can be enabled. The ON/OFF-state of WRx is determined by the SMB charger.</td></uvlo<> | >UVLO | High   | Hi-Z  | Load switch = OFF, and OTG mode can be enabled. The ON/OFF-state of WRx is determined by the SMB charger. |

| =UVLO                                                                                                                                                                              | =VOUT | Low    | Low   | Load switch = ON, and OTG mode are enabled. The ON/OFF-state of WRx is determined by the SMB charger.     |

| >UVLO                                                                                                                                                                              | Low   | Low X  |       | Load switch = ON (EN_N = High), and OTG mode is not allowed.                                              |

Figure 4. FLAG\_N Block Diagram and Functionality

## Input OVP and Reverse Current Blocking

In the OFF-state (non-conducting), the load switch USBIN to ground withstand voltage is at least 28VDC with a reverse blocking voltage of at least 16VDC. In the ON-state (conducting), the load switch maximum  $V_{\text{USBIN}}/V_{\text{OUT}}$  to ground operating voltage is at least 20VDC.

#### Soft-Start

Bidirectional peak current limiting is provided with a 0.8ms soft-start that occurs during load switch activation. In slave mode, soft-start when a valid EN\_N pin is toggled and after the debounce delay is satisfied. In autonomous mode, soft-start when a valid FLAG\_N pin is toggled and after the debounce delay and break-before-make plus discharge delay is satisfied.

## **Input Surge Protection**

The device must withstand up to 120V surge voltage applied from the USBIN pin to ground pins. The surge may be applied to the load switch in the ON/OFF-state. The surge waveform is compatible with the IEC

61000-4-5 specification,  $R_{\text{SOURCE}}$  = 2.0 $\Omega$ , 1.2/50 $\mu$ s waveform.

Figure 5. Surge Voltage Waveform with  $C_{USBIN} = 1\mu F$ Capacitive Loading

#### **OTG Modes**

OTG modes occur after the charger detects an OTG plug-in event, ~5V is applied to the OUT pin, and the USBIN pin is tied to an OTG load. The USB\_SNS and EN\_N pins are used in slave mode, while the FLAG\_N pin is used in autonomous mode as shown in Figure 6.

Figure 6. OTG Mode (R-OTG Load Applied to USBIN, Autonomous Mode)

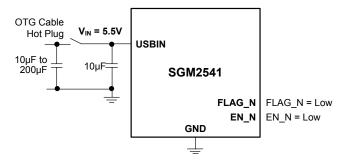

OTG mode must support  $C_{OUT}$  = 1 $\mu$ F (static), plus  $C_{OTG}$  = 200 $\mu$ F that can occur during a hot plug event; see Figure 7.

Figure 7. OTG Cable Capacitive Hot Plug Event (C-Load Applied)

#### **Debounce Period**

The valid USBIN detection occurs after a 50ms input debounce period. There is no OUT debounce.

## **Turn-On Delay and Discharge**

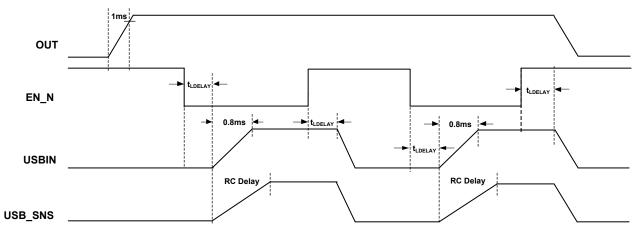

In autonomous mode, the USBIN 50ms debounce period is followed by a 50ms break-before-make delay that allows time to disable the device while discharging the wireless Rx output. The break-before-make delay is

also triggered in autonomous mode when RX\_N = High. These delays are followed by a 0.8ms soft-start to limit peak inrush currents.

A 10mA (or  $500k\Omega$ ) pull-down at OUT is active during the 50ms break-before-make delay, ensuring that no voltage appears at the output when the ON-state is activated.

The break-before-make delay is inactive when the  $V_{USBIN}$  is removed because UVLO is active and the load switch is not powered; see Figure 9.

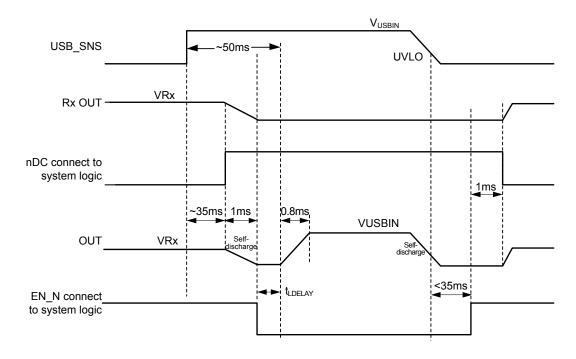

## **Timing Diagrams**

Figure 8 to Figure 11 show slave and autonomous mode timing diagrams.

In slave mode, the ON/OFF-state of the load switch is determined by the EN\_N logic input pin that is tied to the system logic. The wireless Rx ON/OFF-state is determined by an external connection between the system logic and the wireless Rx enable input shown as nDC. A 0.8ms soft-start delay is applied when the EN\_N pin is toggled Low, and the USBIN 50ms debounce period has expired.

Figure 8. Slave Mode Timing (with Battery Present): Dual Input with USBIN Insertion and Removal (Assumes FLAG\_N = Iow, RX\_N = Low)

In autonomous mode, a 50ms debounce delay, 50ms break-before-make/discharge period and a 0.8ms soft-start delay are applied when the USB\_SNS input is rising threshold is detected. The FLAG\_N pin provides

the USBIN voltage status prior to entering OTG mode. The discharge feature is enabled during the 50ms break-before-make period.

Figure 9. Autonomous Mode Timing: Dual Input with USBIN Insertion and Removal (Assumes EN\_N = low)

In OTG modes, a load is applied to the USBIN and current flow from OUT to USBIN.

In slave mode, OTG occurs when a valid OUT voltage is applied, no voltage is detected at the USB\_SNS and the  $t_{\text{LDELAY}}$  debounce time is satisfied. OTG mode is triggered by pulling the EN\_N pin low, as shown in Figure 9.

In autonomous mode, the FLAG\_N is a logic output and toggles high to indicate USBIN invalid, and OTG can be enabled immediately. The FLAG\_N pin is bidirectional, and autonomous OTG mode is triggered by pulling the FLAG\_N input pin low, which triggers a soft start.

Figure 10. Slave OTG Mode Timing: OTG Activate and Deactivate (Assumes FLAG\_N = low, RX\_N = low)

Figure 11. Autonomous OTG Mode Timing: OTG Activate and Deactivate (Assumes EN\_N = low)

# PACKAGE OUTLINE DIMENSIONS WLCSP-2.43×1.75-20B

NOTE: All linear dimensions are in millimeters.

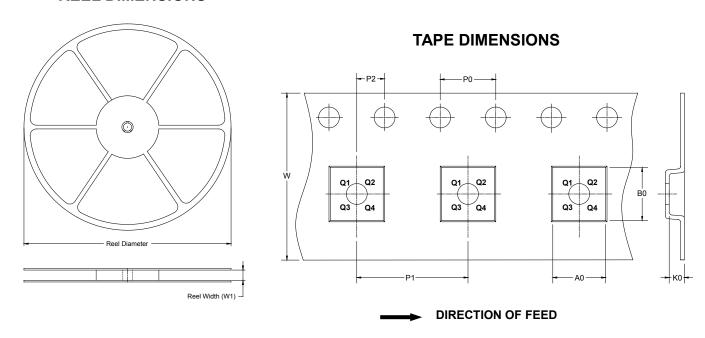

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type        | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| WLCSP-2.43×1.75-20B | 7"               | 9.2                      | 1.90       | 2.71       | 0.81       | 4.0        | 4.0        | 2.0        | 8.0       | Q2               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width Height (mm) |     | Pizza/Carton |  |

|-------------|----------------|-------------------|-----|--------------|--|

| 7" (Option) | 368            | 227               | 224 | 8            |  |

| 7"          | 442            | 410               | 224 | 18           |  |