# TPS61253A, TPS61253E 3.8-MHz, 5-V, 4-A Boost Converter in 1.2-mm x 1.3-mm WCSP

#### 1 Features

- Wide input voltage range from 2.3 V to 5.5 V (TPS61253A)

- Wide input voltage range from 2.5 V to 5.5 V (Startup>2.6V, TPS61253E)

- Fixed output voltage: 4.5 / 4.7 / 5.0 / 5.2 V / 5.25 V

- Two FETs integrated: 35-mΩ LS-FET, 60-mΩ HS-

- IOUT ≥ 1500-mA continuously at VOUT = 5 V and VIN ≥ 3 V (TPS61253A)

- IOUT ≥ 1500-mA continuously at VOUT = 5.25 V and VIN ≥ 3 V (TPS61253E)

- 42-µA quiescent current from input

- 4-A switching valley current limit

- 3.8-MHz switching frequency

- Selectable auto PFM, forced PWM, and ultrasonic

- Support pass-through mode

- ±2% output voltage accuracy

- 600-us soft-start time

- Hiccup-mode short protection

- Load disconnection during shutdown

- Thermal shutdown

- Total solution size < 25 mm<sup>2</sup>

- Create a custom design using the TPS61253A with the WEBENCH® Power Designer

#### 2 Applications

- **Smart phones**

- Portable speaker

- USB charging ports

- NFC PA supply

- Li battery to 5-V power conversion

#### 3 Description

The TPS61253x device provides a power supply solution for battery-powered portable applications. With the input voltage ranging from 2.3 V to 5.5 V (TPS61253A) or 2.5 V to 5.5 V (TPS61253E), the device supports the applications powered by the Li-lon batteries with the extended voltage range. Different fixed output voltage versions are available of 4.5 V. 4.7 V. 5 V. 5.2V and 5.25 V. The TPS61253x supports up to 1500-mA load current from a battery discharged as low as 3 V.

The TPS61253x operates at typical 3.8-MHz switching frequency. The TPS61253x can be flexibly configured at the Auto PFM mode, forced PWM mode, or ultrasonic mode. The Auto PFM mode can benefit with the high efficiency at the light load. The forced PWM operation can make the switching frequency be constant crossing the whole load range. The ultrasonic mode keeps the switching frequency always larger than 25 kHz at any load condition to avoid the acoustic noise.

TPS61253x has a built-in 600-µs soft start to avoid the inrush current at start-up. When the output is shorted, the device enters into the hiccup mode and recovers automatically after the short releases. During the shutdown, the load is completely disconnected from the input end with maximum 1.3-µA current being consumed.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM) |

|-------------|------------------------|-----------------|

| TPS61253x   | DSBGA (9)              | 1.2 mm × 1.3 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

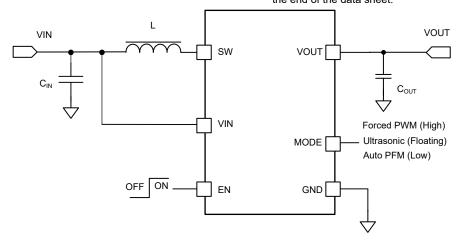

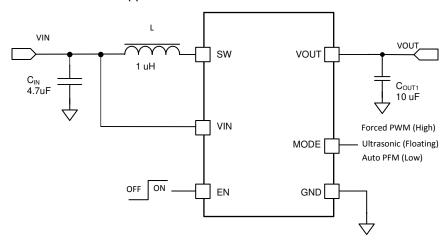

**Typical Schematic**

# **Table of Contents**

| 1 Features                                                      | 1              | 8.3 Feature Description                      |      |

|-----------------------------------------------------------------|----------------|----------------------------------------------|------|

| 2 Applications                                                  | 1              | 8.4 Device Functional Modes                  | 15   |

| 3 Description                                                   | 1              | 9 Application and Implementation             | 17   |

| 4 Revision History                                              | 2              | 9.1 Application Information                  | 17   |

| 5 Device Comparison                                             | <mark>3</mark> | 9.2 Typical Application                      | 17   |

| 6 Pin Configuration and Functions                               | 4              | 10 Layout                                    | 24   |

| 7 Specifications                                                | <u>5</u>       | 10.1 Layout Guidelines                       | 24   |

| 7.1 Absolute Maximum Ratings                                    |                | 10.2 Layout Example                          |      |

| 7.2 ESD Ratings                                                 |                | 10.3 Thermal Considerations                  |      |

| 7.3 Recommended Operating Conditions                            | <mark>5</mark> | 11 Device and Documentation Support          |      |

| 7.4 Thermal Information                                         |                | 11.1 Device Support                          | 25   |

| 7.5 Electrical Characteristics                                  | 6              | 11.2 Documentation Support                   |      |

| 7.6 Timing Requirements                                         | 8              | 11.3 Receiving Notification of Documentation |      |

| 7.7 Switching Characteristics                                   |                | 11.4 Support Resources                       |      |

| 7.8 Typical Characteristics                                     |                | 11.5 Trademarks                              |      |

| 8 Detailed Description                                          |                | 11.6 Electrostatic Discharge Caution         |      |

| 8.1 Overview                                                    |                | 11.7 Glossary                                |      |

| 8.2 Functional Block Diagram                                    |                | ,                                            |      |

| 4 Revision History NOTE: Page numbers for previous revisions ma | ay differ fi   | om page numbers in the current version.      |      |

| Changes from Revision D (January 2021) to I                     | Revision       | E (June 2023)                                | Page |

| TPS61253E initial release                                       |                |                                              | 1    |

| Changes from Revision C (November 2020) t                       | o Revisi       | on D (January 2021)                          | Page |

| Adding HS FET to the functional block diagra                    | <br>am         |                                              | 13   |

# **5 Device Comparison**

| PART<br>NUMBER            | OUTPUT<br>VOLTAGE | SW VALLEY<br>CURRENT LIMIT<br>(TYP.) | DC START-UP<br>CURRENT<br>LIMT (TYP.) | INPUT START-<br>UP VOLTGAE | EN I/O LOGIC                            | SPECIFIC FEATURES                                                 |

|---------------------------|-------------------|--------------------------------------|---------------------------------------|----------------------------|-----------------------------------------|-------------------------------------------------------------------|

| TPS61253A                 | 5 V               | 4 A                                  | 1.5 A                                 | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 5 V, up to 1500 mA                                |

| TPS612532A                | 5 V               | 4 A                                  | 1.5 A                                 | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 5 V, up to 1500 mA with output discharge function |

| TPS61254A <sup>(1)</sup>  | 4.5 V             | 2.5 A                                | 0.75 A                                | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 4.5 V, up to 1000 mA                              |

| TPS61255A <sup>(1)</sup>  | 4.7 V             | 4 A                                  | 1.5 A                                 | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 4.5 V, up to 1500 mA                              |

| TPS612561A <sup>(1)</sup> | 5 V               | 2.5 A                                | 0.75 A                                | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 5 V, up to 1000 mA                                |

| TPS61258A <sup>(1)</sup>  | 4.5 V             | 4 A                                  | 1.5 A                                 | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 4.5 V, up to 1500 mA                              |

| TPS612592A <sup>(1)</sup> | 5.2 V             | 4 A                                  | 0.75 A                                | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 5.2 V, up to 1500 mA                              |

| TPS612531A <sup>(1)</sup> | 5 V               | 4 A                                  | 1.5 A                                 | 2.3 V                      | Supports 1.8 V logic I/O                | Supports output 5 V, up to 1500 mA with PFM/PWM mode only         |

| TPS61253E                 | 5.25 V            | 4.5 A                                | 1.5 A                                 | 2.6 V                      | Supports both 1.8 V and 1.2 V logic I/O | Supports output 5.25 V,<br>up to 1500 mA                          |

<sup>(1)</sup> Preview. Contact TI factory for more information.

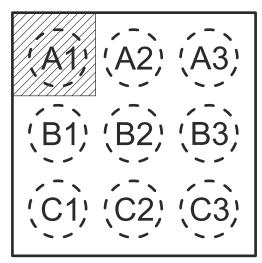

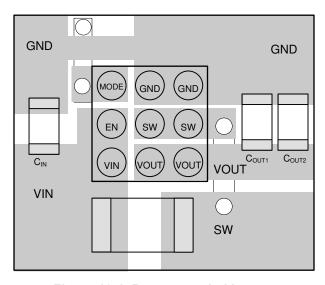

# **6 Pin Configuration and Functions**

Figure 6-1. 9-Pin DSBGA YFF Package (Top View)

Table 6-1. Pin Functions

| P    | PIN    |     | PIN                                                                                                                                                                                                                                                                                                                                                                                                                   |  | PIN I/O |  | DESCRIPTION |

|------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------|--|-------------|

| NAME | NO.    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           |  |         |  |             |

| EN   | В3     | I   | This is the enable pin of the device. Connecting this pin to ground forces the device into shutdown mode. Pulling this pin high enables the device. There is an internal resistor pulled to GND.                                                                                                                                                                                                                      |  |         |  |             |

| GND  | C1, C2 | _   | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                            |  |         |  |             |

| MODE | C3     | -   | Operation mode selection pin  Mode = Low, the device works in the Auto PFM mode with good light load efficiency.  Mode = High, the device is in the forced PWM mode, keep the switching frequency be constant crossing the whole load range.  Mode = Floating, the device works in the ultrasonic mode; it keeps the switching frequency larger than 25 kHz to avoid the acoustic frequency toward no load condition. |  |         |  |             |

| sw   | B1, B2 | I/O | The switch pin of the converter. It is connected to the drain of the internal low-side power FET and the source of the internal high-side power FET.                                                                                                                                                                                                                                                                  |  |         |  |             |

| VIN  | A3     | I   | Power supply input                                                                                                                                                                                                                                                                                                                                                                                                    |  |         |  |             |

| VOUT | A1, A2 | 0   | Boost converter output                                                                                                                                                                                                                                                                                                                                                                                                |  |         |  |             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                | MIN  | MAX | UNIT |

|---------------------------------------|--------------------------------|------|-----|------|

| Valtage range at terminals            | Voltage at VIN, EN, MODE, VOUT | -0.3 | 6   | V    |

| Voltage range at terminals            | Voltage at SW                  | -0.3 | 7   | V    |

| Storage temperature, T <sub>stg</sub> |                                | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

# 7.3 Recommended Operating Conditions

Over operating free-air temperature range unless otherwise noted.

|                  |                                | MIN  | NOM | MAX | UNIT |

|------------------|--------------------------------|------|-----|-----|------|

| \/               | Input voltage (TPS61253A)      | 2.3  |     | 5.5 | V    |

| V <sub>IN</sub>  | Input voltage (TPS61253E)      | 2.5  |     | 5.5 | V    |

| L                | Effective inductance           | 0.33 |     | 1.3 | μH   |

| C <sub>OUT</sub> | Effective output capacitance   | 3.5  | 5   | 30  | μF   |

| TJ               | Operating junction temperature | -40  |     | 125 | °C   |

#### 7.4 Thermal Information

|                       |                                              | TPS61253x   |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC(1)                            | YFF (DSBGA) | UNIT |

|                       |                                              | 9 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 108.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 1.2         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 28.8        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.6         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 28.9        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 7.5 Electrical Characteristics

For TPS61253A,  $V_{IN}$  = 2.3 V to 4.85 V ,  $V_{OUT}$  = 5 V ,  $T_J$  = -40°C to 125°C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25°C, unless otherwise noted.

For TPS61253E,  $V_{IN}$  = 2.6 V to 4.85 V ,  $V_{OUT}$  = 5.25 V ,  $T_J$  = -40°C to 125°C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25°C, unless otherwise noted.

|                      | PARAMETER                                                    | TEST CONDITIONS                                                                                                                             | MIN   | TYP   | MAX   | UNIT              |

|----------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| SUPPLY (             | CURRENT                                                      |                                                                                                                                             |       |       |       |                   |

|                      | Input voltage under voltage                                  | V <sub>IN</sub> rising, TPS61253A                                                                                                           |       | 2.2   | 2.3   | V                 |

| $V_{IN\_UVLO}$       | lockout (UVLO) threshold                                     | V <sub>IN</sub> falling, TPS61253A                                                                                                          |       | 2.1   | 2.2   | V                 |

|                      | Input voltage under voltage                                  | V <sub>IN</sub> rising, TPS61253E                                                                                                           | 2.4   | 2.5   | 2.6   | V                 |

|                      | lockout (UVLO) threshold (E version)                         | V <sub>IN</sub> falling, TPS61253E                                                                                                          | 2.3   | 2.4   | 2.5   | V                 |

| 1                    | Quiescent current into VIN pin                               | $V_{\rm IN}$ = 3.6 V, $V_{\rm OUT}$ = 5V , EN = $V_{\rm IN}$ Device not switching                                                           |       | 42    | 50    | μΑ                |

| IQ                   | Quiescent current into VOUT pin                              | $V_{\text{IN}}$ = 3.6 V, $V_{\text{OUT}}$ = 5V , EN = $V_{\text{IN}}$ Device not switching                                                  |       | 6.6   | 12    | μΑ                |

| I <sub>SD</sub>      | Shutdown current                                             | EN = GND , $V_{IN}$ = 2.3 V to 5.5 V, $-40~^{\circ}\text{C} \le T_{J}$ $\le 85 ^{\circ}\text{C}$                                            |       | 0.05  | 1.3   | μΑ                |

| OUTPUT               | VOLTAGE                                                      |                                                                                                                                             |       |       |       |                   |

|                      | PWM Operation                                                | $2.3 \text{ V} \le \text{V}_{\text{IN}} \le 4.85 \text{V}, \text{I}_{\text{OUT}} = 0 \text{mA}, \text{PWM}$ operation. Open Loop. TPS61253A | 4.9   | 5     | 5.1   | V                 |

| V <sub>OUT</sub>     | PWM Operation                                                | $2.6 \text{ V} \le \text{V}_{\text{IN}} \le 4.85 \text{V}, \text{I}_{\text{OUT}} = 0 \text{mA}, \text{PWM}$ operation. Open Loop. TPS61253E | 5.145 | 5.25  | 5.355 | V                 |

|                      | PFM Operation                                                | Auto PFM Mode                                                                                                                               |       | 100.8 |       | %V <sub>OUT</sub> |

|                      | Ultrasonic Operation                                         | Ultrasonic Mode                                                                                                                             |       | 101.6 |       | %V <sub>OUT</sub> |

| R <sub>DIS</sub>     | output discharge resistor                                    | VOUT = 5 V, TPS612532A                                                                                                                      |       | 350   |       | Ω                 |

| POWER S              | SWITCHES                                                     |                                                                                                                                             |       |       |       |                   |

| D                    | Low-side FET on resistance                                   |                                                                                                                                             |       | 35    | 55    | mΩ                |

| R <sub>DSON</sub>    | High-side FET on resistance                                  |                                                                                                                                             |       | 60    | 80    | mΩ                |

| CURREN               | T LIMIT                                                      |                                                                                                                                             |       |       | '     |                   |

|                      | Switching valley current limit at Auto PFM / Ultrasonic Mode | TPS61253A                                                                                                                                   | 3.4   | 4     | 4.6   | А                 |

|                      | Switching valley current limit at Forced PWM Mode            | TPS61253A                                                                                                                                   | 3.35  | 3.95  | 4.55  | Α                 |

| I <sub>LIM_</sub> SW | Switching valley current limit at Auto PFM / Ultrasonic Mode | TPS61253E                                                                                                                                   | 3.9   | 4.5   | 5.1   | Α                 |

|                      | Switching valley current limit at Forced PWM Mode            | TPS61253E                                                                                                                                   | 3.85  | 4.45  | 5.05  | Α                 |

| I <sub>LIM_DC</sub>  | DC startup current limit                                     | TPS61253A, TPS61253E                                                                                                                        | 1     | 1.5   |       | Α                 |

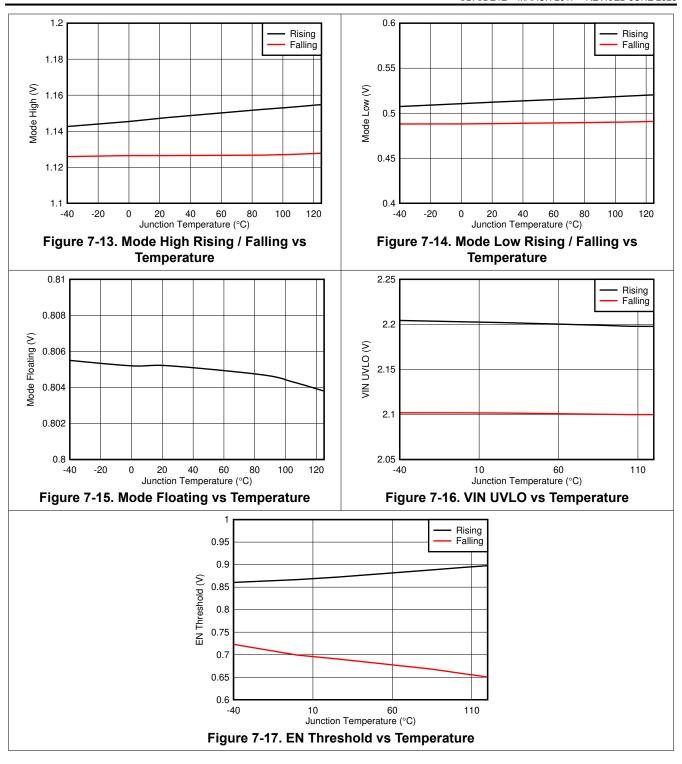

| EN AND N             | MODE LOGIC                                                   |                                                                                                                                             |       |       | '     |                   |

|                      | EN la via biola de carata da                                 | TPS61253A                                                                                                                                   |       |       | 1.2   | V                 |

| $V_{EN\_H}$          | EN logic high threshold                                      | TPS61253E                                                                                                                                   |       |       | 0.9   | V                 |

| \ /                  | EN Jamie Jamié des de la la                                  | TPS61253A                                                                                                                                   | 0.4   |       |       | V                 |

| $V_{EN\_L}$          | EN logic low threshold                                       | TPS61253E                                                                                                                                   | 0.36  |       |       | V                 |

| R <sub>EN</sub>      | EN pull-down resistor                                        |                                                                                                                                             |       | 930   |       | kΩ                |

| V <sub>MODE_H</sub>  | Mode logic high threshold                                    |                                                                                                                                             |       |       | 1.2   | V                 |

| V <sub>MODE_L</sub>  | Mode logic low threshold                                     |                                                                                                                                             | 0.4   |       |       | V                 |

| V <sub>MODE_F</sub>  | Mode pin floating voltage                                    |                                                                                                                                             | 0.75  | 0.8   | 0.85  | V                 |

| I <sub>MODE_UP</sub> | Pull up current                                              |                                                                                                                                             |       | 1     |       | μA                |

# **TPS61253A, TPS61253E** SLVSDE4E – MARCH 2017 – REVISED JUNE 2023

| PARAMETER            |                                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |  |

|----------------------|-----------------------------------|-----------------|-----|-----|-----|------|--|--|

| I <sub>MODE_DO</sub> | Pull down current                 |                 | 1   |     | μA  |      |  |  |

| PROTECT              | PROTECTION                        |                 |     |     |     |      |  |  |

| T <sub>SD_R</sub>    | Thermal shutdown rising threshold |                 |     | 150 |     | °C   |  |  |

| T <sub>SD_HYS</sub>  | Thermal protection hysteresis     |                 |     | 20  |     | °C   |  |  |

#### 7.6 Timing Requirements

For TPS61253A,  $V_{IN}$  = 2.3 V to 4.85 V ,  $V_{OUT}$  = 5 V ,  $T_J$  = –40 °C to 125 °C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25 °C, unless otherwise noted.

For TPS61253E,  $V_{IN}$  = 2.6 V to 4.85 V ,  $V_{OUT}$  = 5.25 V ,  $T_J$  = -40 °C to 125 °C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25 °C, unless otherwise noted.

|                       |                              |                                                 | MIN NOM | MAX | UNIT |  |  |  |

|-----------------------|------------------------------|-------------------------------------------------|---------|-----|------|--|--|--|

| HICCUP (              | HICCUP OFF TIME              |                                                 |         |     |      |  |  |  |

| t <sub>HCP_ON</sub>   | Hiccup on time               | V <sub>IN</sub> = 3.6 V                         | 1000    |     | μs   |  |  |  |

| t <sub>HCP_OFF</sub>  | Waiting time for the restart | V <sub>IN</sub> = 3.6 V                         | 20      |     | ms   |  |  |  |

| START U               | START UP TIME                |                                                 |         |     |      |  |  |  |

| t <sub>EN_DELAY</sub> | Startup delay time           | Time from EN high to start switching, No load   | 70      |     | μs   |  |  |  |

| t <sub>SS</sub>       | Soft start time              | Time from EN high to V <sub>OUT</sub> , No load | 600     |     | μs   |  |  |  |

# 7.7 Switching Characteristics

For TPS61253A,  $V_{IN}$  = 2.3 V to 4.85 V ,  $V_{OUT}$  = 5 V ,  $T_J$  = –40 °C to 125 °C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25 °C, unless otherwise noted.

For TPS61253E,  $V_{IN}$  = 2.6 V to 4.85 V ,  $V_{OUT}$  = 5.25 V ,  $T_J$  = -40 °C to 125 °C ; Typical values are at  $V_{IN}$  = 3.6 V ,  $T_J$  = 25 °C, unless otherwise noted.

| PARAMETER       |                                      | TEST CONDITIONS         | MIN | TYP MA | X UNIT |

|-----------------|--------------------------------------|-------------------------|-----|--------|--------|

|                 | Switching frequency, PWM mode        | V <sub>IN</sub> = 3.6 V |     | 3800   | kHz    |

| f <sub>SW</sub> | Switching frequency, Ultrasonic mode | V <sub>IN</sub> = 3.6 V | 25  |        | kHz    |

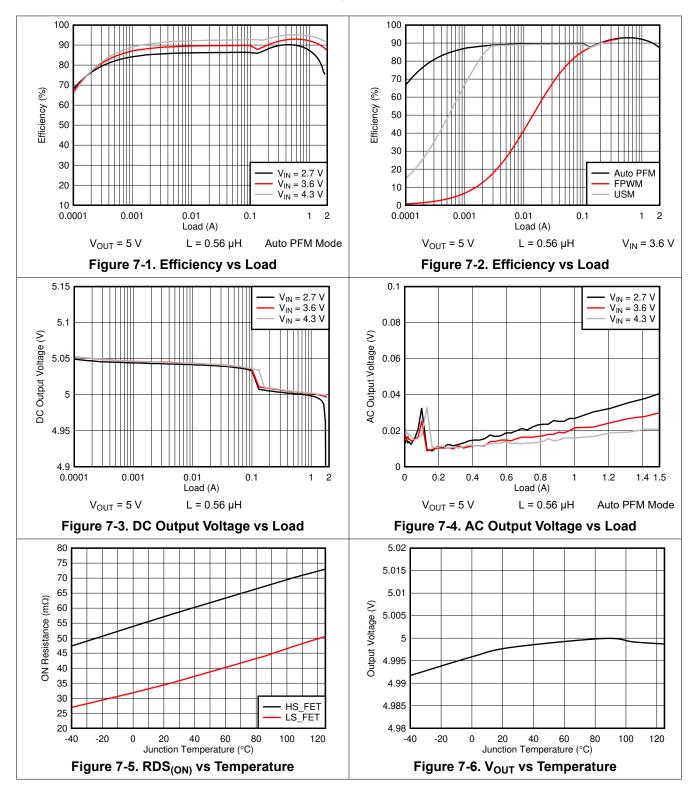

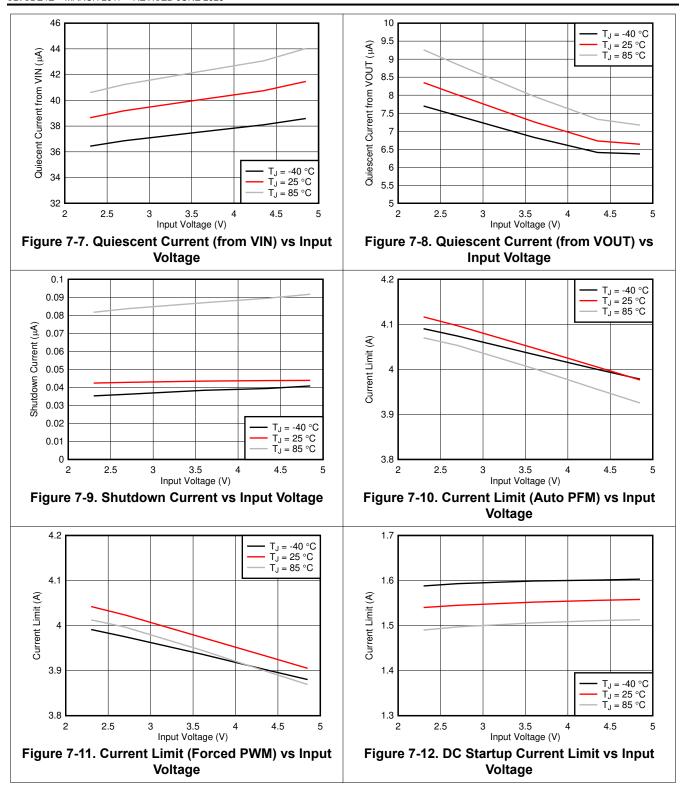

# 7.8 Typical Characteristics

This section is based on the test results of TPS61253A, unless otherwise noted.

# **8 Detailed Description**

#### 8.1 Overview

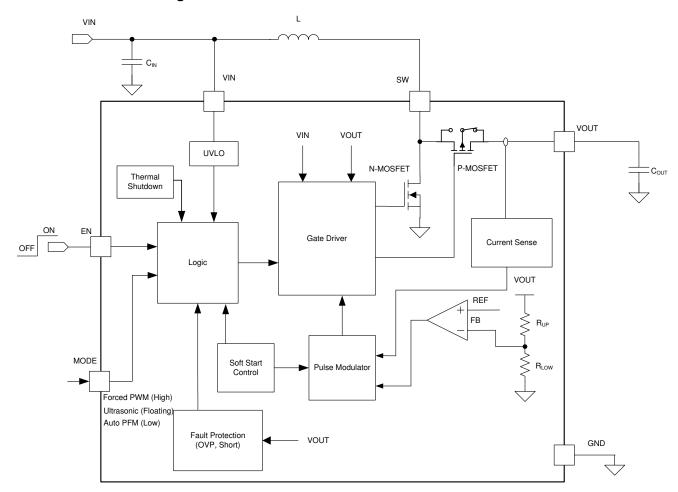

The TPS61253x synchronous step-up converter typically operates at a quasi-constant 3.8-MHz frequency pulse width modulation (PWM) from the moderate-to-heavy load currents. During the PWM operation, the converter uses a quasi-constant on-time valley current mode control scheme to achieve the excellent line / load regulation and allows the use of a small inductor and ceramic capacitors. Based on the  $V_{\text{IN}}$  /  $V_{\text{OUT}}$  ratio, a simple circuit predicts the required on-time. At the beginning of the switching cycle, the low-side N-MOS switch is turned on and the inductor current ramps up to a peak current that is defined by the on-time and the inductance. In the second phase, once the on-timer has expired, the rectifier FET is turned on and the inductor current decays to a preset valley current threshold. Then, the switching cycle repeats by setting the on timer again and activating the low-side N-MOS switch.

At the light load current conditions, the TPS61253x can be flexibly configured at the Auto PFM mode, the forced PWM or the ultrasonic mode. At the Auto PFM mode, the TPS61253x converter operates in Power Save Mode with pulse frequency modulation (PFM) and improves the efficiency. For forced PWM mode, the switching frequency is the same at the light load as that of heavy load. The ultrasonic mode is a unique control feature that keeps the switching frequency above 25 kHz to avoid the acoustic audible frequencies toward virtually no load condition.

In general, a dc/dc step-up converter can only operate in "true" boost mode, that is the output "boosted" by a certain amount above the input voltage. The TPS61253x device operates differently as it can smoothly transition in and out of pass-through operation ( $V_{IN}$  exceeds the preset out of Boost). Therefore the output can be kept as close as possible to its regulation limits even though the converter is subject to an input voltage that tends to be excessive.

Internal soft start and loop compensation simplify the design process while minimizing the number of external components.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Start-up

The TPS61253x integrates an internal circuit that controls the ramp up of the output voltage during start-up and prevents the converter from the large inrush current. When the device is enabled, the high-side rectifying switch turns on to charge the output capacitor linearly which is called the pre-charge phase. During the pre-charge phase, the output current is limited to the pre-charge current limit ILIM\_DC. The pre-charge phase terminates until the output voltage getting close to the input voltage.

Once the output capacitor has been biased close to the input voltage, the device starts switching which is called the soft-start phase. During the soft start phase, there is a soft-start voltage controlling the FB pin voltage, and the output voltage rising slope follows the soft-start voltage slope. The device finishes the soft-start phase and operates normally when the nominal output voltage is reached.

Table 8-1. Start-up Mode Description

|            | MODE             | DESCRIPTION                                           | CONDITION                                                            |  |  |  |

|------------|------------------|-------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| Pre-charge |                  | V <sub>OUT</sub> linearly starts up without switching | V <sub>OUT</sub> < V <sub>IN</sub> - 300 mV                          |  |  |  |

|            | Boost soft start | V <sub>OUT</sub> starts up wih switching phrase       | V <sub>OUT_BOOST</sub> ≥ V <sub>OUT</sub> ≥ V <sub>IN</sub> - 300 mV |  |  |  |

#### 8.3.2 Enable and Disable

The device is enabled by setting EN pin to a voltage above 1.2 V (TPS61253A) or 0.9 V (TPS61253E) and  $V_{IN}$  above UVLO threshold. At first, the internal reference is activated and the internal analog circuits are settled. Afterwards, the start-up is activated and the output voltage ramps up. With the EN pin pulled to ground, the

device enters shutdown mode. In shutdown mode, the TPS61253x stops switching and the internal control circuitry is turned off.

#### 8.3.3 Undervoltage Lockout (UVLO)

The undervoltage lockout circuit prevents the device from malfunctioning at the low input voltage of the battery from the excessive discharge. The device starts operation once the rising  $V_{IN}$  trips the undervoltage lockout (UVLO) threshold and it disables the output stage of the converter once the  $V_{IN}$  is below UVLO falling threshold.

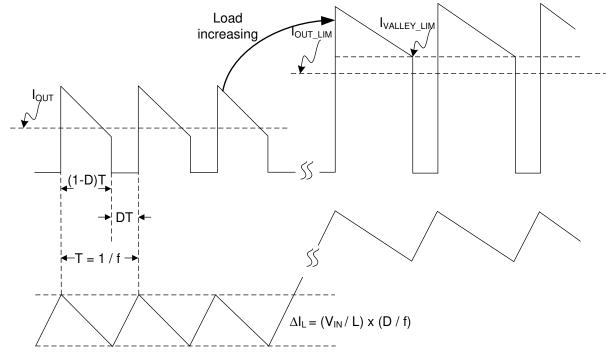

#### 8.3.4 Current Limit Operation

During the start-up phase, the output current is limited to the pre-charge current limit which is specified as the ILIM DC in Section 7.5.

The TPS61253x employs a valley current sensing scheme at the normal boost switching phase. When the output load is increased, the cycle-by-cycle valley current limit will be triggered. As shown in Figure 8-1, the maximum continuous output current, prior to entering the current limit operation, can be defined by Equation 1:

$$I_{OUT\_LIM} \quad (1-D) \times (I_{VALLEY\_LIM} + \frac{1}{2}\Delta I_{L})$$

(1)

$$D = 1 - \frac{V_{IN} \times \eta}{V_{OUT}}$$

(2)

$$\Delta I_{L} = \frac{V_{IN}}{L} \times \frac{D}{f}$$

(3)

#### where

- I<sub>OUT LIM</sub> is the output current limit, I<sub>VALLEY LIM</sub> is switching valley current limit

- Δ<sub>IL</sub> is the peak-peak inductor current ripple

- D is the duty cycle, f is the switching frequency, η is the efficiency, L is the inductor

- V<sub>OUT</sub> is the output voltage, V<sub>IN</sub> is the input voltage

Figure 8-1. Current Limit Operation

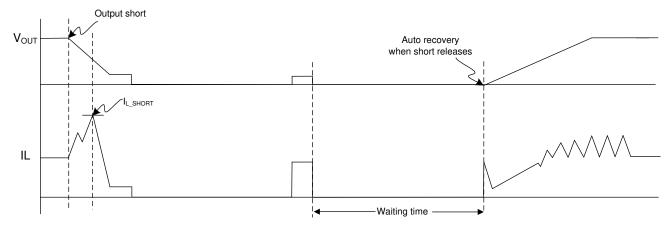

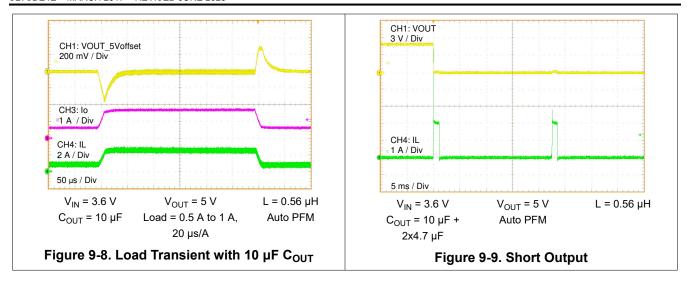

If the output current is further increased and triggers the short protection threshold (typical 6 A of inductor current), the TPS61253x enters into hiccup mode. Once the hiccup is triggered, the device turns on the high-side FET for around 1 ms with the pre-charge current limit and stops for around 20 ms. The hiccup on / off cycle repeats again and again if the short condition is present. Figure 8-2 illustrates the TPS61253x working scheme of the hiccup mode. The average current and thermal will be much lowered at the hiccup steady state and the device can recover automatically as long as the short releases.

Figure 8-2. Hiccup Mode Short Protection

#### 8.3.5 Load Disconnection

The advantage of TPS61253x is that this converter disconnects the output from the input of the power supply when it is disabled. In case of a connected battery, it prevents it from being discharged during shutdown of the converter.

#### 8.3.6 Thermal Shutdown

The TPS61253x has a built-in temperature sensor that monitors the internal junction temperature,  $T_J$ . If the junction temperature exceeds the threshold (typical 150 °C), the device goes into the thermal shutdown, and the high-side and low-side FETs are turned off. When the junction temperature falls below the thermal shutdown falling threshold (typical 130 °C), the device resumes the operation.

#### 8.4 Device Functional Modes

# 8.4.1 Auto PFM Mode

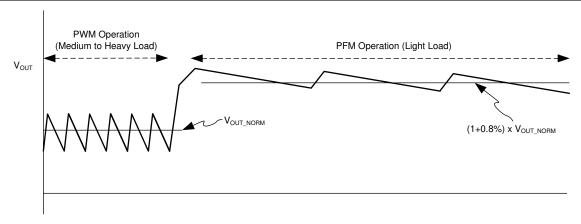

The device integrates Power Save Mode with pulse frequency modulation (Auto PFM) to improve the efficiency at the light load. At the light load operation, when the valley current of the inductor triggers the Auto PFM threshold, the device enters into Auto PFM mode operation. During the Auto PFM operation, the output voltage is regulated at typically 100.8% of voltage of the heavy load with the off-time extended to lower the switching frequency. The Auto PFM operation exists when valley current exceeds the Auto PFM threshold. Figure 8-3 shows the output voltage behavior of Auto PFM operation.

Figure 8-3. Output Voltage in Auto PFM / PWM Mode

#### 8.4.2 Forced PWM Mode

In forced PWM mode, the TPS61253x keeps the switching frequency being constant for the whole load range. When the load current decreases, the output of the internal error amplifier decreases as well to lower the inductor peak current and delivers less power from input to output. The high-side FET is not turned off even if the current through the FET goes negative to keep the switching frequency being the same as that of the heavy load.

#### 8.4.3 Ultrasonic Mode

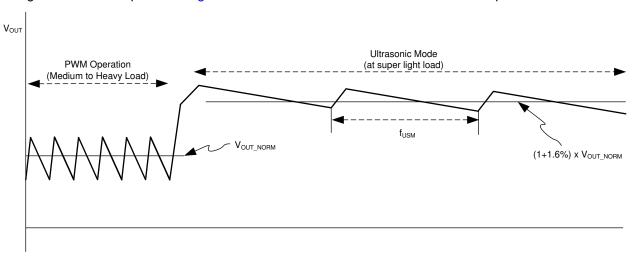

The ultrasonic mode is an unique control feature that keeps the switching frequency above the acoustic audible frequency toward no load condition. The ultrasonic mode control circuit monitors the switching frequency and keeps the switching frequency above 25 kHz to avoid the acoustic band. The output voltage becomes typically 1.6% higher than PWM operation. Figure 8-4 illustrates the details of ultrasonic mode operation.

Figure 8-4. Ultrasonic Mode Operation

#### 8.4.4 Pass-Through Mode

When the input voltage is higher than  $V_{OUT}$  + 0.1 V and  $V_{OUT}$  is higher than the nominal output voltage, the device automatically enters Pass-Through mode. In Pass-Through mode, the high-side FET is fully turned on and the low-side switch is turned off. The output voltage follows the input with the drop caused by the inductor resistance and the high-side FET resistance.

# 9 Application and Implementation

#### **Note**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 9.1 Application Information

With a wide input voltage range, the TPS61253x supports applications powered by Li-Ion batteries with extended voltage range. Intended for the low-power applications, it supports up to 1500-mA load current from a battery discharged as low as 3 V and allows the use of low cost chip inductor and capacitors. The TPS61253x offers a very small solution size due to minimum amount of external components. It allows the use of small inductors and input capacitors to achieve a small solution size. During the pass-through mode, the output voltage is biased to the input voltage.

#### 9.2 Typical Application

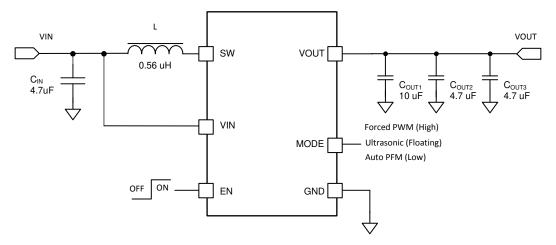

Figure 9-1. Typical Application Circuit

#### 9.2.1 Design Requirements

In this example, TPS61253x is used to design a 5-V output Boost converter. The TPS61253x can be powered by one-cell Li-ion battery. It supports up to 1500-mA output current from the input voltage as low as 3.0 V. During shutdown, the load is completely disconnected from the battery.

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS61253x device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- · Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

· Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Inductor Selection

A boost converter normally requires two main passive components for storing energy during the conversion, an inductor and an output capacitor. It is advisable to select an inductor with a saturation current rating higher than the possible peak current flowing through the power switches.

The inductor peak current varies as a function of the load, the input and output voltages. It can be estimated using Equation 4.

$$I_{L(PEAK)} = \frac{V_{IN} \cdot D}{2 \cdot f \cdot L} + \frac{I_{OUT}}{(1-D)} \quad \text{with} \quad D = 1 - \frac{V_{IN} \cdot \eta}{V_{OUT}}$$

(4)

Selecting an inductor with insufficient saturation current can lead to excessive peak current in the converter. This could eventually harm the device and reduce its reliability. When selecting the inductor, as well as the inductance, parameters of importance are: the maximum current rating, series resistance, and operating temperature. The inductor DC current rating should be greater (by some margin) than the maximum input average current, refer to Equation 5 for more details.

$$I_{L(DC)} = \frac{V_{OUT}}{V_{IN}} \cdot \frac{1}{\eta} \cdot I_{OUT}$$

(5)

The TPS61253x series of step-up converters could support operating with an effective inductance in the range of 0.33  $\mu$ H to 1.3  $\mu$ H and with effective output capacitance in the range of 3.5  $\mu$ F to 30  $\mu$ F. The internal compensation is optimized for an output filter of the inductance between 0.56  $\mu$ H and 1  $\mu$ H and output capacitance from 5  $\mu$ F to 10  $\mu$ F. Larger or smaller inductor and capacitor values can be used to optimize the performance of the device for specific operating conditions. For more details, see *Section 9.2.2.5*.

In high-frequency converter applications, the efficiency is essentially affected by the inductor AC resistance (that is, quality factor) and to a smaller extent by the inductor DCR value. To achieve high efficiency operation, care should be taken in selecting inductors featuring a quality factor above 25 at the switching frequency. Increasing the inductor value produces lower RMS current, but degrades transient response. For a given physical inductor size, increased inductance usually results in an inductor with lower saturation current.

The total losses of the coil consist of both the losses in the DC resistance, R(DC), and the following frequency dependent components:

- The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- · Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- Magnetic field losses of the neighboring windings (proximity effect)

- · Radiation losses

The following inductor series from different suppliers have been used with the TPS61253x converters.

**Table 9-1. List of Inductors**

| MANUFACTURER <sup>(1)</sup> |                         | SERIES         | DESCRIPTION                                        | DIMENSIONS (W × L × H)   |  |  |

|-----------------------------|-------------------------|----------------|----------------------------------------------------|--------------------------|--|--|

|                             | Colicraft               | XEL3515-561MEB | $0.56~\mu H$ , $21.5~m\Omega$ DCR, $6.5~A~I_{sat}$ | 3.2 mm × 3.5 mm × 1.5 mm |  |  |

|                             | Murata 1277AS-H-1R0M=P2 |                | 1 μH, 34 mΩ DCR, 4.6 A I <sub>sat</sub>            | 3.2 mm × 2.5 mm × 1.2 mm |  |  |

(1) See Section 11.1.1.

#### 9.2.2.3 Output Capacitor

For the output capacitor, it is recommended to use small ceramic capacitors placed as close as possible to the VOUT and GND pins of the IC. If, for any reason, the application requires the use of large capacitors which cannot be placed close to the IC, using a smaller ceramic capacitor in parallel to the large one is highly recommended. This small capacitor should be placed as close as possible to the VOUT and GND pins of the IC. To get an estimate of the recommended minimum output capacitance, Equation 6 can be used.

$$C_{MIN} = \frac{I_{OUT} \cdot (V_{OUT} - V_{IN})}{f \cdot \Delta V \cdot V_{OUT}}$$

(6)

where

- f is the switching frequency which is 3.8 MHz (typ.)

- ΔV is the maximum allowed output ripple

With a chosen ripple voltage of 25 mV, a minimum effective capacitance of 7  $\mu$ F is needed for maximum 1500-mA load. The capacitor can be smaller if the load is lower or the ripple can be larger. The total ripple is larger due to the ESR of the output capacitor. This additional component of the ripple can be calculated using Equation 7

$$V_{ESR} = I_{OUT} \cdot R_{ESR} \tag{7}$$

An MLCC capacitor with twice the value of the calculated minimum should be used due to DC bias effects. This is required to maintain control loop stability. The output capacitor requires either an X7R or X5R dielectric. Y5V and Z5U dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies. There are no additional requirements regarding minimum ESR. Larger capacitors cause lower output voltage ripple as well as lower output voltage drop during load transients but the total effective output capacitance value should not exceed ca.  $30 \, \mu F$ .

DC bias effect: high cap. ceramic capacitors exhibit DC bias effects, which have a strong influence on the effective capacitance of the device. Therefore, the right capacitor value has to be chosen very carefully. Package size and voltage rating in combination with material are responsible for differences between the rated capacitor value and effective capacitance. For instance, a 10- $\mu$ F X5R 6.3-V 0603 MLCC capacitor would typically show an effective capacitance of less than 4  $\mu$ F under 5 V bias condition.

#### 9.2.2.4 Input Capacitor

Multilayer ceramic capacitors are an excellent choice for input decoupling of the step-up converter since they have extremely low ESR and are available in small footprints. Input capacitors should be located as close as possible to the device. While a 4.7-µF input capacitor is sufficient for most applications, larger values can be used to reduce input current ripple without limitations.

Take care when using only ceramic input capacitors. When a ceramic capacitor is used at the input and the power is being supplied through long wires, such as from a wall adapter, a load step at the output can induce ringing at the VIN pin. This ringing can couple to the output and be mistaken as loop instability or could even damage the part. Additional "bulk" capacitance (electrolytic or tantalum) should in this circumstance be placed between  $C_{IN}$  and the power source lead to reduce ringing that can occur between the inductance of the power source leads and  $C_{IN}$ .

#### 9.2.2.5 Checking Loop Stability

The first step of circuit and stability evaluation is to look from a steady-state perspective at the following signals:

- Switching node, SW

- Inductor current, I<sub>I</sub>

- Output ripple voltage, V<sub>OUT(AC)</sub>

These are the basic signals that need to be measured when evaluating a switching converter. When the switching waveform shows large duty cycle jitter or the oscillation happens for the output voltage or inductor current, the regulation loop can be unstable. This is often a result of board layout, L-C combination, or both.

As a next step in the evaluation of the regulation loop, the load transient response is tested. The time between the application of the load transient and the turn on of the high-side FET, the output capacitor must supply all of the current required by the load.  $V_{OUT}$  immediately shifts by an amount equal to  $\Delta I_{(LOAD)}$  × ESR, where ESR is

#### TPS61253A, TPS61253E

SLVSDE4E - MARCH 2017 - REVISED JUNE 2023

the effective series resistance of  $C_{OUT}$ .  $\Delta I_{(LOAD)}$  begins to charge or discharge  $C_{OUT}$  generating a feedback error signal used by the regulator to return  $V_{OUT}$  to its steady-state value. The results are most easily interpreted when the device operates in PWM mode.

During this recovery time,  $V_{OUT}$  can be monitored for settling time, overshoot, or ringing that helps judge the stability of the converter. Without any ringing, the loop has usually more than 45° of phase margin. Because the damping factor of the circuitry is directly related to several resistive parameters (for example, MOSFET  $r_{DS(on)}$ ) that are temperature dependent, the loop stability analysis has to be done over the input voltage range, load current range, and temperature range.

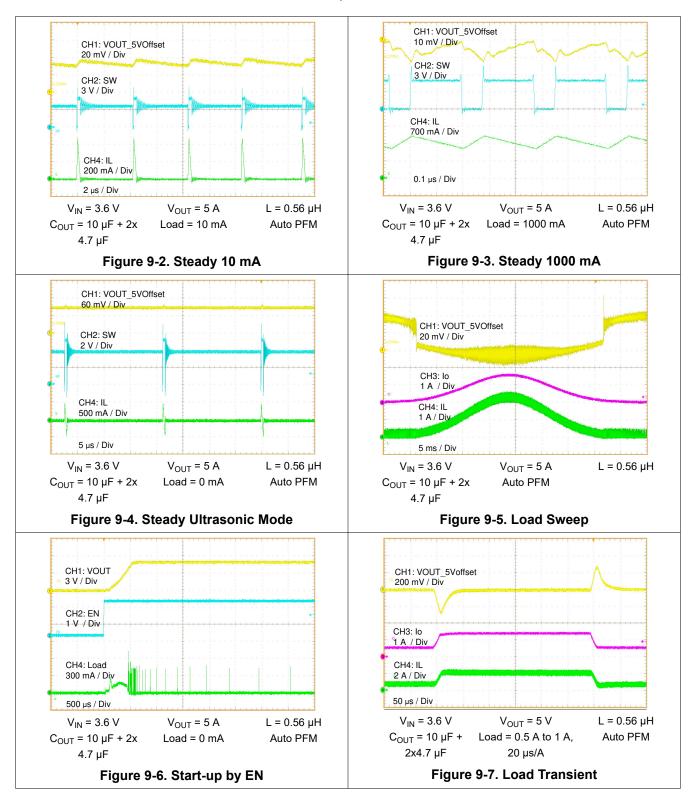

#### 9.2.2.6 Application Curves

This section is based on the test results of TPS61253A, unless otherwise noted.

#### 9.2.3 System Examples

For the < 1000 mA output current application, the output capacitors could be less. Figure 9-10 shows the typical application circuit for the lower current applications.

Figure 9-10. Typical Application with Minimum Output Capacitance

# **Power Supply Recommendations**

The power supply can be three-cell alkaline, NiCd or NiMH, or one-cell Li-lon or Li-Polymer battery. The input supply should be well regulated with the rating of TPS61253x. If the input supply is located more than a few inches from the device, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. An electrolytic or tantalum capacitor with a value of  $47 \, \mu F$  is a typical choice.

#### 10 Layout

#### 10.1 Layout Guidelines

For all switching power supplies, the layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the regulator can show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path and for the power ground tracks. The input capacitor, output capacitor, and the inductor should be placed as close as possible to the IC. Use a common ground node for power ground and a different one for control ground to minimize the effects of ground noise. Connect these ground nodes at any place close to the ground pins of the IC.

#### 10.2 Layout Example

Figure 10-1. Recommended Layout

#### 10.3 Thermal Considerations

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

The following are three basic approaches for enhancing thermal performance:

- Improving the power dissipation capability of the PCB design

- Improving the thermal coupling of the component to the PCB

- · Introducing airflow in the system

As power demand in portable designs is more and more important, designers must figure the best tradeoff between efficiency, power dissipation and solution size. Due to integration and miniaturization, junction temperature can increase significantly which could lead to bad application behaviors (that is, premature thermal shutdown or worst case reduce device reliability).

Junction-to-ambient thermal resistance is highly dependent on application and board-layout. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design. The device operating junction temperature (T<sub>1</sub>) should be kept below 125°C.

# 11 Device and Documentation Support

#### 11.1 Device Support

# 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 11.1.2 Development Support

#### 11.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS61253x device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , and output current  $(I_{OUT})$  requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

# 11.2 Documentation Support

#### 11.2.1 Related Documentation

For related documentation see the following:

TPS61253AEVM-803 User's Guide, SLVUAP5

#### 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 11.5 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

#### 11.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# 11.7 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

# Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |            |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| TPS612532AYFFR   | ACTIVE     | DSBGA        | YFF                | 9    | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | 2CHI                    | Samples |

| TPS61253AYFFR    | ACTIVE     | DSBGA        | YFF                | 9    | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | 17NI                    | Samples |

| TPS61253AYFFT    | ACTIVE     | DSBGA        | YFF                | 9    | 250            | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | 17NI                    | Samples |

| TPS61253EYFFR    | ACTIVE     | DSBGA        | YFF                | 9    | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | 32UH                    | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

# **PACKAGE OPTION ADDENDUM**

15-Aug-2023

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS WHO WE PI WHO WE PI WHO WE BO WE Cavity A O WE Cavity

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

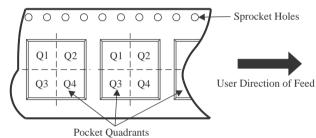

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS612532AYFFR | DSBGA           | YFF                | 9 | 3000 | 180.0                    | 8.4                      | 1.31       | 1.41       | 0.69       | 4.0        | 8.0       | Q1               |

| TPS61253AYFFR  | DSBGA           | YFF                | 9 | 3000 | 180.0                    | 8.4                      | 1.31       | 1.41       | 0.69       | 4.0        | 8.0       | Q1               |

| TPS61253AYFFT  | DSBGA           | YFF                | 9 | 250  | 180.0                    | 8.4                      | 1.31       | 1.41       | 0.69       | 4.0        | 8.0       | Q1               |

| TPS61253EYFFR  | DSBGA           | YFF                | 9 | 3000 | 180.0                    | 8.4                      | 1.31       | 1.41       | 0.69       | 4.0        | 8.0       | Q1               |

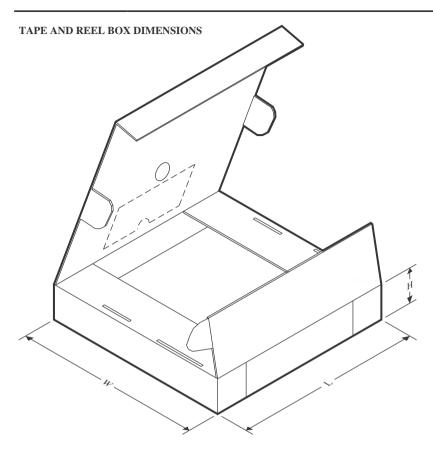

# PACKAGE MATERIALS INFORMATION

5-Dec-2023

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS612532AYFFR | DSBGA        | YFF             | 9    | 3000 | 182.0       | 182.0      | 20.0        |

| TPS61253AYFFR  | DSBGA        | YFF             | 9    | 3000 | 182.0       | 182.0      | 20.0        |

| TPS61253AYFFT  | DSBGA        | YFF             | 9    | 250  | 182.0       | 182.0      | 20.0        |

| TPS61253EYFFR  | DSBGA        | YFF             | 9    | 3000 | 182.0       | 182.0      | 20.0        |

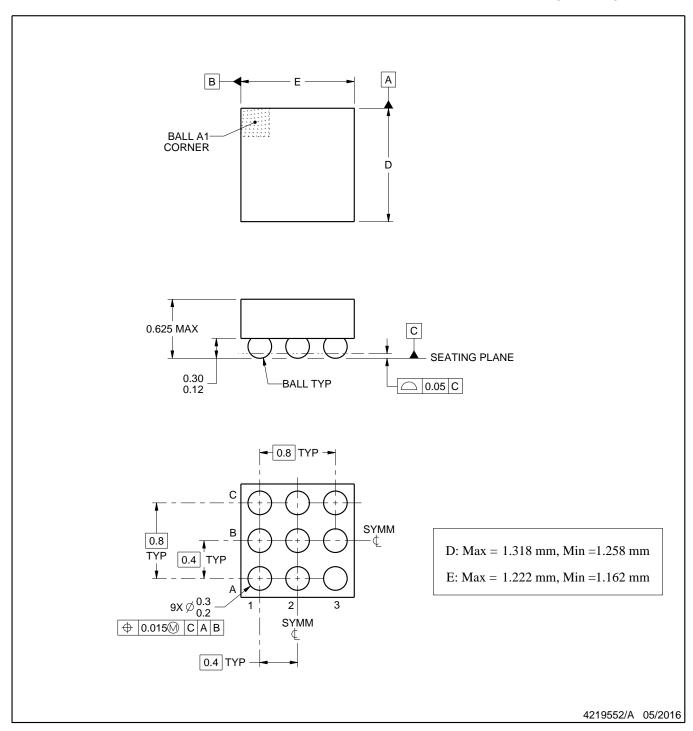

DIE SIZE BALL GRID ARRAY

#### NOTES:

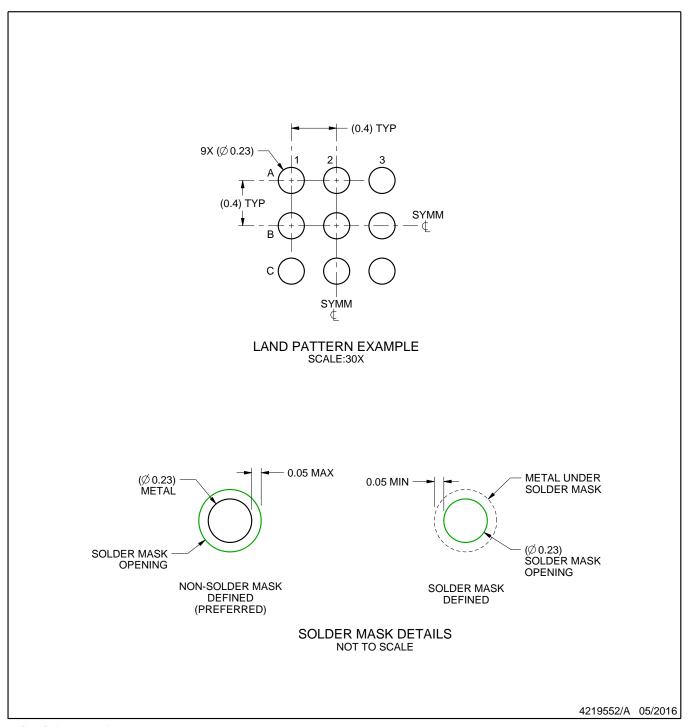

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

3. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. For more information, see Texas Instruments literature number SNVA009 (www.ti.com/lit/snva009).

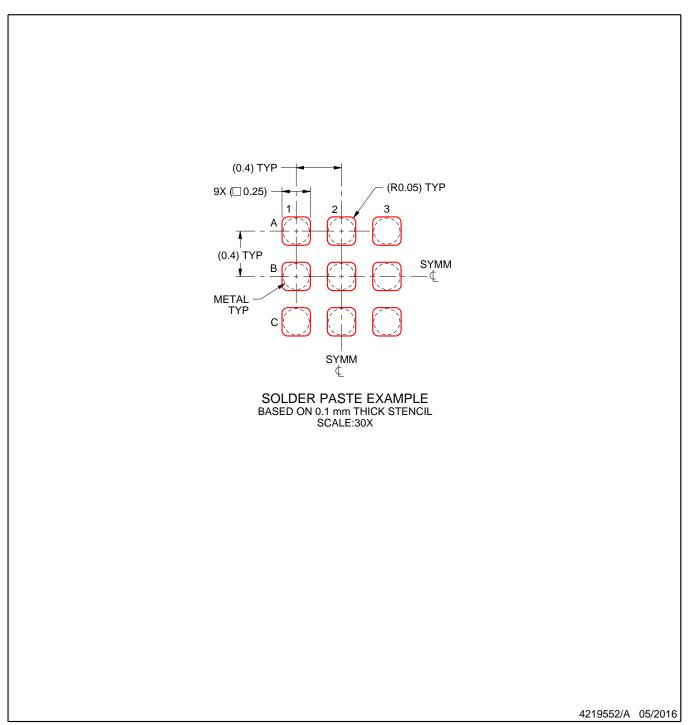

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.