## SMBus NVDC Buck-Boost Battery Charge Controller with System Power Monitor and Processor Hot Monitor

#### **FEATURES**

- 1- to 4-Cell Charging from a Variety of Input Types

- 3.58V to 24V Input Operating Voltage Range

- USB 2.0/3.0/3.1 (Type C)/USB-PD Input Current Support

- Seamless Buck ↔ Buck-Boost ↔ Boost Transitions

- Input Overload Protection (IDPM and VDPM Regulation)

- CPU Throttling, Power and Current Monitoring

- Full nPROCHOT Profile IMVP8/IMVP9 Compliant

- · Input Current Monitoring

- Battery Charge/Discharge Current Monitoring

- System Power Monitoring, IMVP8/IMVP9 Compliant

- Narrow Voltage DC (NVDC) Power Path Management

- · Instant-On with Depleted or No Battery

- Battery Supplementation if Adapter is Fully Loaded

- BATFET Ideal Diode Emulation in Supplement Mode

- Power-Up USB Port from Battery (USB OTG)

- 3V to 20.56V Adjustable OTG Voltage with 8mV Resolution

- Up to 6.35A Output Current Limit with 50mA Resolution

- Pass Through Mode (PTM) to Improve Efficiency

- V<sub>MIN</sub> Active Protection (VAP) Mode

- VAP Supplements Battery from Input Caps for System Power Spikes (Battery-Only Conditions)

- Input Current Optimizer Maximizes Power Extraction

- 800kHz or 1.2MHz Selectable Switching Frequency

- SMBus Interface for Flexible System Configuration

- Input Current Limit Setting Pin (without SMBus)

- Integrated ADC for Voltage/Current/Power Monitoring

- Low Battery Quiescent Current

- High Accuracy

- TBD% for Charge Voltage Regulation

- TBD% for Input/Charge Current Regulation

- TBD% for Input/Charge Current Monitor

- TBD% for Power Monitor

- Safety

- Thermal Shutdown

- Input/System/Battery Over-Voltage Protection

- Input/MOSFET/Inductor Over-Current Protection

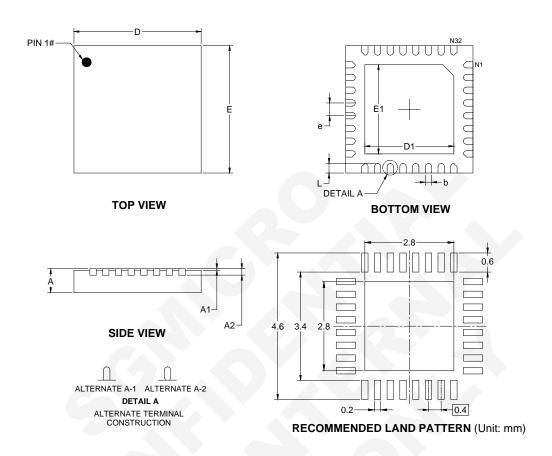

- Available in a Green TQFN-4×4-32AL Package

### **APPLICATIONS**

Bluetooth Speakers, Drones, IP Cameras, Detachable Power Supply

Portable Internet Devices and Accessory Industrial and Medical Equipment

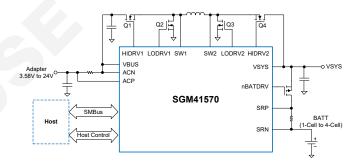

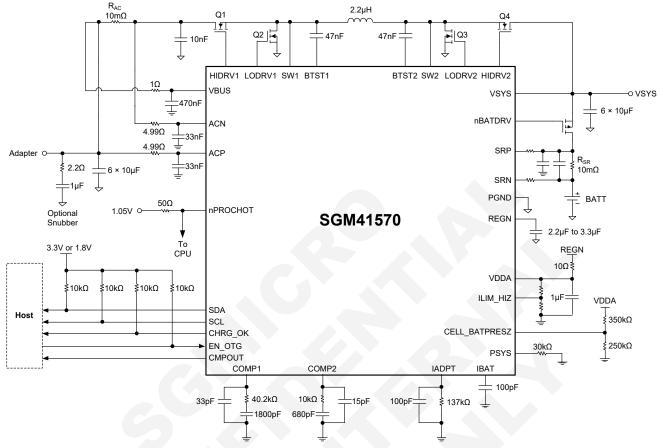

### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

## SMBus Narrow VDC Buck-Boost Battery Charge Controller with System Power Monitor and Processor Hot Monitor

### **GENERAL DESCRIPTION**

The SGM41570 is a synchronous Buck-Boost battery charge controller with NVDC power path management. It can provide high efficiency and low component count solution for 1-cell to 4-cell battery charging applications.

The system is regulated slightly above battery voltage and not below the programmable system minimum voltage. Therefore, system power is maintained even if the battery is completely depleted or removed. Dynamic power management (DPM) feature is also included that automatically reduces the charge current if the input current or voltage limit is reached. If the system load continues to increase after reduction of charge current down to zero, the battery goes into supplement mode and both adapter and battery power the system.

A wide range of input sources are supported for SGM41570, including traditional adapters, USB adapter and high voltage USB PD sources. Depending on the input source and battery conditions, the converter is configured as Buck, Boost or Buck-Boost during power-up. The charger automatically transition among Buck, Boost and Buck-Boost and requires no host control.

When input source is absent, SGM41570 can work in USB On-The-Go (OTG) mode to supply VBUS from battery. The OTG output voltage can be programmed from 3V to 20.56V with 8mV resolution, and the output voltage transition slew rate can be configurable, which is complied with the USB PD 3.0 PPS specifications.

If there is no external load on the USB OTG port and the system is powered by battery only, the  $V_{\text{MIN}}$  Active Protection (VAP) feature is supported. In VAP, the VBUS voltage is charged up by the battery and the energy is stored in the input decoupling capacitors. When the system demands power spike, the stored energy will supplement the system to prevent the system voltage from dropping below the minimum system voltage.

Adapter current, battery current and system power are monitored in SGM41570. When system power is too high and exceeds available power from adapter and battery together, a flexibly programmed nPROCHOT pulse is asserted to inform CPU for throttle back.

## SMBus Narrow VDC Buck-Boost Battery Charge Controller with System Power Monitor and Processor Hot Monitor

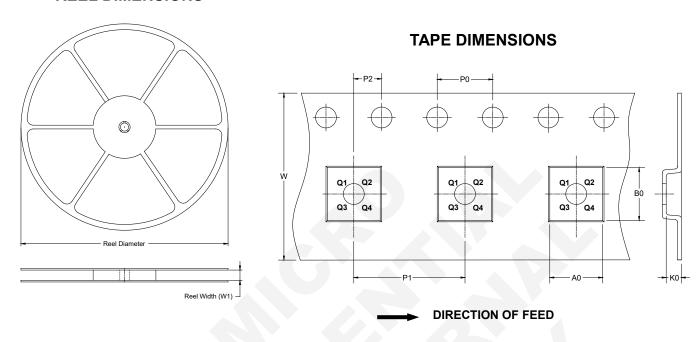

#### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|-----------------------------|---------------------|

| SGM41570 | TQFN-4×4-32AL          | -40°C to +125°C                   | SGM41570XTSE32G/TR | SGM41570<br>XTSE32<br>XXXXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range (with Respect to GND) |                   |

|-------------------------------------|-------------------|

| SRN, SRP, ACN, ACP, VBUS, VSYS      | 0.3V to 30V       |

| SW1, SW2                            | 2V to 30V         |

| BTST1, BTST2, HIDRV1, HIDRV2, nE    | BATDRV            |

|                                     | 0.3V to 36V       |

| LODRV1, LODRV2 (25ns)               |                   |

| HIDRV1, HIDRV2 (25ns)               |                   |

| SW1, SW2 (25ns)                     | 4V to 30V         |

| SDA, SCL, REGN, PSYS, CHRG_OK       | X, OTG/VAP,       |

| CELL_BATPRESZ, ILIM_HIZ, LODR\      | /1, LODRV2, VDDA, |

| nPROCHOT, CMPIN, CMPOUT             |                   |

|                                     | 0.3V to 7V        |

| COMP1, COMP2                        |                   |

| IADPT, IBAT, PSYS                   | 0.3V to 3.6V      |

| Differential Voltage                |                   |

| BTST1-SW1, BTST2-SW2, HIDRV1-S      | SW1, HIDRV2-SW2   |

|                                     | 0.3V to 7V        |

| SRP-SRN, ACP-ACN                    | 0.5V to 0.5V      |

| Package Thermal Resistance          |                   |

| TQFN-4×4-32AL, θ <sub>JA</sub>      |                   |

| Junction Temperature                | +150°C            |

| Storage Temperature Range           |                   |

| Lead Temperature (Soldering, 10s)   | +260°C            |

|                                     |                   |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### RECOMMENDED OPERATING CONDITIONS

| Voltage Range (with Respect to GND)     |                  |

|-----------------------------------------|------------------|

| ACN, ACP, VBUS                          | 0V to 24V        |

| SRN, SRP, VSYS                          | 0V to 19.2V      |

| SW1, SW2                                | 2V to 24V        |

| BTST1, BTST2, HIDRV1, HIDRV2, nB/       | ATDRV            |

|                                         | 0V to 30V        |

| SDA, SCL, REGN, PSYS, CHRG_OK           | , CELL_BATPRESZ, |

| ILIM_HIZ, LODRV1, LODRV2, VDDA          | A, COMP1, COMP2, |

| CMPIN, CMPOUT                           |                  |

|                                         | 0V to 6.5V       |

| nPROCHOT                                | 0V to 5.3V       |

| IADPT, IBAT, PSYS                       | 0V to 3.3V       |

| Differential Voltage Range (with Respec | t to GND)        |

| BTST1-SW1, BTST2-SW2, HIDRV1-SV         | W1, HIDRV2-SW2   |

|                                         | 0V to 6.5V       |

| SRP-SRN, ACP-ACN                        | 0.5V to 0.5V     |

| Operating Junction Temperature Range.   | 40°C to +85°C    |

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## SMBus Narrow VDC Buck-Boost Battery Charge Controller with System Power Monitor and Processor Hot Monitor

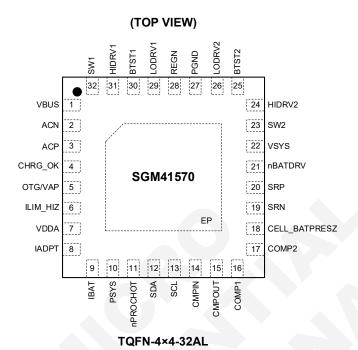

### PIN CONFIGURATION

### **PIN DESCRIPTION**

| PIN | NAME     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VBUS     | PWR  | Charger Input. Place an RC low pass filter on this pin (R = $1\Omega$ and C $\ge 0.47\mu$ F).                                                                                                                                                                                                                                                                                                                                                           |

| 2   | ACN      | PWR  | Negative Terminal of the Input Current Sense Resistor. Place an RC low pass filter between this pin and the sense resistor. The leakage current on ACN and ACP are matched.                                                                                                                                                                                                                                                                             |

| 3   | ACP      | PWR  | Positive Terminal of the Input Current Sense Resistor. Place an RC low pass filter between this pin and the sense resistor. The leakage current on ACN and ACP are matched.                                                                                                                                                                                                                                                                             |

| 4   | CHRG_OK  | 0    | Active High Open-Drain Good Power Source Status Output. Place a $10k\Omega$ resistor between this pin and pull-up rail. CHRG_OK goes high after 50ms deglitch time when VBUS rises above 3.58V or falls below 23.9V. CHRG_OK goes low when VBUS falls below 3.21V or rises above 25.8V.                                                                                                                                                                 |

| 5   | OTG/VAP  | ı    | OTG or VAP Modes Enable Input (Active High). OTG mode enable: OTG_VAP_MODE bit = 1, EN_OTG bit = 1 and pull this pin to high. VAP mode enable: OTG_VAP_MODE bit = 0, and pull this pin to high.                                                                                                                                                                                                                                                         |

|     |          |      | Input Current Limit Setting Input. Connect this pin to a resistor divider between supply and ground to set the target input current limit I <sub>DPM</sub> using the following equation:                                                                                                                                                                                                                                                                |

| 6   | ILIM_HIZ | 1    | $V_{ILIM\_HIZ} = 1V + 40 \times I_{DPM} \times R_{AC}$                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |          |      | The actual input current limit is the lower setting of ILIM_HIZ pin and IIN_HOST register. The device enters HIZ mode when $V_{\text{ILIM}\_HIZ} < V_{\text{HIZ}\_LOW}$ , and exits HIZ mode when $V_{\text{ILIM}\_HIZ} > V_{\text{HIZ}\_HIGH}$ .                                                                                                                                                                                                       |

| 7   | VDDA     | PWR  | Internal Reference Bias. Place a $10\Omega$ resistor from REGN to this pin, and place a $1\mu F$ ceramic capacitor from this pin to ground.                                                                                                                                                                                                                                                                                                             |

| 8   | IADPT    | 0    | Adapter Current Monitoring Output. $V_{IADPT}$ = 20 or 40 × ( $V_{ACP}$ - $V_{ACN}$ ) and 20 or 40 can be selected in the IADPT_GAIN bit. Place a resistor corresponding to the inductance in use from this pin to ground. The resistor is 137k $\Omega$ when L = 2.2 $\mu$ H. Connect a 100pF or less ceramic decoupling capacitor from this pin to ground. IADPT output voltage is clamped below $V_{IADPT\_CLAMP}$ .                                 |

| 9   | IBAT     | 0    | Battery Current Monitoring Output. The charge current is monitored as $V_{IBAT} = 8$ or $16 \times (V_{SRP} - V_{SRN})$ , and discharge current is monitored as $V_{IBAT} = 8$ or $16 \times (V_{SRN} - V_{SRP})$ , 8 or 16 can be selected in the IBAT_GAIN bit. Connect a 100pF or less ceramic decoupling capacitor from this pin to ground. IBAT pin can be left floating if not in use and its output voltage is clamped below $V_{IBAT\_CLAMP}$ . |

# **SMBus Narrow VDC Buck-Boost Battery Charge Controller** with System Power Monitor and Processor Hot Monitor

## **PIN DESCRIPTION (continued)**

| PIN            | NAME          | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10             | PSYS          | 0    | System Power Monitoring Output (Current Mode). The output current of this pin is proportional to the total power from the adapter and the battery. The gain is selectable through SMBus. Place a resistor from this pin to ground to generate output voltage. PSYS pin can be left floating if not in use and its output voltage is clamped below $V_{\text{PSYS\_CLAMP}}$ .                                                                                                                                         |

| 11             | nPROCHOT      | 0    | Active Low Open-Drain Processor Hot Indicator Output. The adapter input current, battery discharge current and system voltage are monitored, and a pulse is asserted if any event in the nPROCHOT profile is triggered. The minimum pulse width is adjustable in PROCHOT_WIDTH[1:0] bits.                                                                                                                                                                                                                            |

| 12             | SDA           | I/O  | SMBus Data Signal. Use a $10k\Omega$ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13             | SCL           | I    | SMBus Clock Signal. Use a $10k\Omega$ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14             | CMPIN         | 1    | Independent Comparator Input. The voltage sensed on this pin is compared with internal reference by the independent comparator, and the output of comparator is on CMPOUT pin. The Internal reference, output polarity and deglitch time are all selectable in the SMBus host. When CMP_POL bit = 1, the internal hysteresis is determined by the resistor between CMPIN and CMPOUT. When CMP_POL bit = 0, the internal hysteresis is 103mV. Connect this pin to ground if the independent comparator is not in use. |

| 15             | CMPOUT        | 0    | Open-Drain Independent Comparator Output. Place a resistor between this pin and pull-up supply rail.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16             | COMP1         | I    | Buck Boost Compensation Pin 1. Refer to Figure 2 for the compensation network.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17             | COMP2         | I    | Buck Boost Compensation Pin 2. Refer to Figure 2 for the compensation network.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18             | CELL_BATPRESZ | 1    | Battery Cell Selection Input. This pin is biased from VDDA, and sets the SYSOVP thresholds (5V for 1-cell, 12V for 2-cell, and 19.4V for 3-cell/4-cell). When the voltage on this pin is pulled below V <sub>CELL_BATPRESZ_FALL</sub> , it indicates battery removal. The device exits LEARN mode, charge is disabled, and the charge voltage register MaxChargeVoltage goes to default.                                                                                                                             |

| 19             | SRN           | PWR  | Negative Input of the Charge Current Sense Resistor. This pin also senses the battery voltage. Place an optional 0.1µF ceramic capacitor from this pin to GND for common-mode noise filtering. Place a 0.1µF ceramic capacitor from SRP to SRN for differential mode noise filtering. The leakage current on SRP and SRN are matched.                                                                                                                                                                                |

| 20             | SRP           | PWR  | Positive Input of the Charge Current Sense Resistor. Place an optional $0.1\mu F$ ceramic capacitor from this pin to GND for common-mode noise filtering. Place a $0.1\mu F$ ceramic capacitor from SRP to SRN for differential mode noise filtering. The leakage current on SRP and SRN are matched.                                                                                                                                                                                                                |

| 21             | nBATDRV       | 0    | P-Channel BATFET Gate Driver Output. It is shorted to VSYS for turning off the BATFET and goes 10V below VSYS for fully on.                                                                                                                                                                                                                                                                                                                                                                                          |

| 22             | VSYS          | PWR  | System Voltage. The system voltage regulation limit is programmed in MaxChargeVoltage registers.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23             | SW2           | PWR  | Boost Mode Switching Node. Connect it to the source of the Boost mode high-side N-channel MOSFET (Q4).                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24             | HIDRV2        | 0    | Boost Mode High-side N-Channel MOSFET (Q4) Driver. Connect to the gate of Q4.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25             | BTST2         | PWR  | Boost Mode High-side N-Channel MOSFET (Q4) Driver Power Supply. Place a 47nF capacitor between SW2 and BTST2. The bootstrap diode between REGN and BTST2 is integrated.                                                                                                                                                                                                                                                                                                                                              |

| 26             | LODRV2        | 0    | Boost Mode Low-side N-Channel MOSFET (Q3) Driver. Connect to the gate of Q3.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 27             | PGND          | GND  | Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28             | REGN          | PWR  | 6V LDO Output. It's supplied from VBUS or VSYS and the LDO is active when VBUS voltage is above $V_{\text{VBUS\_CONVEN}}$ . A 2.2 $\mu$ F or 3.3 $\mu$ F ceramic capacitor is recommended between this pin and PGND.                                                                                                                                                                                                                                                                                                 |

| 29             | LODRV1        | 0    | Buck Mode Low-side N-Channel MOSFET (Q2) Driver. Connect to the gate of Q2.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30             | BTST1         | PWR  | Buck Mode High-side N-Channel MOSFET (Q1) Driver Power Supply. Place a 47nF capacitor between SW1 and BTST1. The bootstrap diode between REGN and BTST1 is integrated.                                                                                                                                                                                                                                                                                                                                               |

| 31             | HIDRV1        | 0    | Buck Mode High-side N-Channel MOSFET (Q1) driver. Connect to the gate of Q1.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 32             | SW1           | PWR  | Buck Mode Switching Node. Connect it to the source of the Buck mode high-side N-channel MOSFET (Q1).                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Exposed<br>Pad | EP            |      | Thermal Pad. It's the thermal pad to conduct heat from the device. Tie externally to the PCB power ground plane. Thermal vias under the pad are needed to conduct the heat to the PCB power ground planes.                                                                                                                                                                                                                                                                                                           |

## **SMBus Narrow VDC Buck-Boost Battery Charge Controller** with System Power Monitor and Processor Hot Monitor

### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                     | SYMBOL                      |                                                    | CONDITIONS                            | MIN   | TYP    | MAX    | UNITS |

|-------------------------------|-----------------------------|----------------------------------------------------|---------------------------------------|-------|--------|--------|-------|

| Input Voltage Operating Range | $V_{INPUT\_OP}$             |                                                    |                                       | 3.58  |        | 24     | V     |

| Regulation Accuracy           |                             |                                                    |                                       |       |        |        |       |

| Max System Voltage Regul      | ation                       |                                                    |                                       |       |        |        |       |

| System Voltage Regulation     | V <sub>SYSMAX_RNG</sub>     | Charge disabled, me                                | easured on V <sub>SYS</sub>           | 1.024 |        | 19.2   | V     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x41A0    |       | 17.02  |        | V     |

|                               |                             |                                                    | (16.800V)                             | TBD   |        | TBD    | %     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x3138    |       | 12.82  |        | V     |

| System Voltage Regulation     |                             | 01                                                 | (12.600V)                             | TBD   |        | TBD    | %     |

| Accuracy                      | V <sub>SYSMAX_ACC</sub>     | Charge disabled                                    | MaxChargeVoltage register = 0x20D0    |       | 8.61   |        | V     |

|                               |                             |                                                    | (8.400V)                              | TBD   |        | TBD    | %     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x1068    |       | 4.41   |        | V     |

|                               |                             |                                                    | (4.200V)                              | TBD   |        | TBD    | %     |

| Minimum System Voltage F      | Regulation                  |                                                    |                                       |       |        |        |       |

| System Voltage Regulation     | V <sub>SYSMIN_RNG</sub>     | Measured on V <sub>SYS</sub>                       |                                       | 1.024 |        | 16.128 | V     |

|                               |                             | Mins                                               | MinSystemVoltage register = 0x3000    |       | 12.27  |        | V     |

|                               |                             |                                                    |                                       | TBD   |        | TBD    | %     |

|                               |                             |                                                    | MinSystemVoltage register = 0x2400    |       | 9.22   |        | V     |

| Minimum System Voltage        |                             | VBAT below<br>MinSystemVoltage<br>register setting |                                       | TBD   |        | TBD    | %     |

| Regulation Accuracy           | V <sub>SYSMIN_REG_ACC</sub> |                                                    | MinSystemVoltage register = 0x1800    |       | 6.16   |        | V     |

|                               |                             |                                                    |                                       | TBD   |        | TBD    | %     |

|                               |                             |                                                    | M. O. A. W. H                         |       | 3.61   |        | V     |

|                               |                             |                                                    | MinSystemVoltage register = 0x0E00    | TBD   |        | TBD    | %     |

| Charge Voltage Regulation     |                             |                                                    |                                       |       |        |        |       |

| Battery Voltage Regulation    | $V_{BAT\_RNG}$              |                                                    |                                       | 1.024 |        | 19.2   | V     |

|                               |                             |                                                    | N 01 N/II 11 0 1100                   |       | 16.788 |        | V     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x41A0    | TBD   |        | TBD    | %     |

|                               |                             |                                                    | Marchanna Vallana na siatan ang 20100 |       | 12.6   |        | V     |

| Battery Voltage Regulation    | V                           | Charge enable                                      | MaxChargeVoltage register = 0x3138    | TBD   |        | TBD    | %     |

| Accuracy                      | V <sub>BAT_REG_ACC</sub>    | (0°C to +85°C)                                     | MayObanna)/altana naniatana 0.2000    |       | 8.407  |        | V     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x20D0    | TBD   |        | TBD    | %     |

|                               |                             |                                                    | M                                     |       | 4.206  |        | V     |

|                               |                             |                                                    | MaxChargeVoltage register = 0x1068    | TBD   |        | TBD    | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                 | SYMBOL                         |                                                                      | CONDITIONS                                        | MIN  | TYP  | MAX   | UNITS |

|-----------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|---------------------------------------------------|------|------|-------|-------|

| Charge Current Regulation in I                            | ast Charge                     |                                                                      |                                                   |      |      |       |       |

| Charge Current Regulation<br>Differential Voltage Range   | V <sub>IREG_CHG_RNG</sub>      | V <sub>IREG_CHG</sub> = V <sub>SRP</sub> - V <sub>SI</sub>           | RN                                                | 0    |      | 81.28 | mV    |

|                                                           |                                |                                                                      | ChargeCurrent register = 0x1000                   |      | 4053 |       | mA    |

|                                                           |                                |                                                                      | Charge Current register – 0x1000                  | TBD  |      | TBD   | %     |

|                                                           |                                | VBAT above                                                           | ChargeCurrent register = 0x0800                   |      | 2019 |       | mA    |

| Charge Current Regulation Accuracy with 10mΩ Sensing      |                                | MinSystemVoltage                                                     | Charge Current register – 0x0000                  | TBD  |      | TBD   | %     |

| Resistor                                                  | I <sub>CHRG_REG_ACC</sub>      | register setting (0°C to +85°C)                                      | ChargeCurrent register = 0x0400                   |      | 999  |       | mA    |

|                                                           |                                | (0 C 10 +65 C)                                                       | Charge outrent register = 0x0400                  | TBD  |      | TBD   | %     |

|                                                           |                                |                                                                      | ChargeCurrent register = 0x0200                   |      | 490  |       | mA    |

|                                                           |                                |                                                                      | Charge Current register – 0x0200                  | TBD  |      | TBD   | %     |

| Charge Current Regulation in I                            | DO Mode                        |                                                                      |                                                   |      |      |       |       |

|                                                           |                                | 2-cell to 4-cell                                                     |                                                   |      | 384  |       | mA    |

| Pre-Charge Current Clamp                                  | I <sub>CLAMP</sub>             | 1-cell, V <sub>SRN</sub> < 3V                                        |                                                   |      | 384  |       | mA    |

|                                                           |                                | 1-cell, 3V < V <sub>SRN</sub> < V                                    | cell, 3V < V <sub>SRN</sub> < V <sub>SYSMIN</sub> |      | 2    |       | Α     |

|                                                           |                                |                                                                      | ChargeCurrent register = 0x0180                   |      | 384  |       | mA    |

|                                                           |                                |                                                                      | 2-cell to 4-cell                                  | TBD  |      | TBD   | %     |

|                                                           |                                | VBAT below<br>MinSystemVoltage<br>register setting<br>(0°C to +85°C) | 1-cell                                            | TBD  |      | TBD   | %     |

|                                                           |                                |                                                                      | ChargeCurrent register = 0x0100                   |      | 256  |       | mA    |

| Pre-Charge Current Regulation                             |                                |                                                                      | 2-cell to 4-cell                                  | TBD  |      | TBD   | %     |

| Accuracy with 10mΩ SRP/SRN                                |                                |                                                                      | 1-cell                                            | TBD  |      | TBD   | %     |

| Series Resistor                                           |                                |                                                                      | ChargeCurrent register = 0x00C0                   |      | 192  |       | mA    |

|                                                           |                                |                                                                      | 2-cell to 4-cell                                  | TBD  |      | TBD   | %     |

|                                                           |                                |                                                                      | 1-cell                                            | TBD  |      | TBD   | %     |

|                                                           |                                |                                                                      | ChargeCurrent register = 0x0080                   |      | 128  |       | mA    |

|                                                           |                                |                                                                      | 2-cell to 4-cell                                  | TBD  |      | TBD   | %     |

| SRP, SRN Leakage Current<br>Mismatch                      | I <sub>LEAK_SRP_SRN</sub>      | 0°C to +85°C                                                         |                                                   | -12  |      | 10    | μΑ    |

| Input Current Regulation                                  |                                |                                                                      |                                                   |      | •    |       |       |

| Input Current Regulation Differential Voltage Range       | V <sub>IREG_DPM_RNG</sub>      | V <sub>IREG_DPM</sub> = V <sub>ACP</sub> - V <sub>A</sub>            | CN                                                | 0.5  |      | 63.5  | mV    |

|                                                           |                                |                                                                      | IIN_HOST register = 0x5000                        | TBD  | 3850 | TBD   |       |

| Input Current Regulation                                  |                                | 1000 1 110500                                                        | IIN_HOST register = 0x3C00                        | TBD  | 2853 | TBD   | mA    |

| Accuracy with $10m\Omega$ ACP/ACN Series Resistor         | DPM_REG_ACC                    | -40°C to +105°C                                                      | IIN_HOST register = 0x1E00                        | TBD  | 1405 | TBD   |       |

|                                                           |                                |                                                                      | IIN_HOST register = 0x0A00                        | TBD  | 448  | TBD   |       |

| ACP, ACN Leakage Current<br>Mismatch                      | I <sub>LEAK_ACP_ACN</sub>      | -40°C to +105°C                                                      |                                                   | -16  |      | 10    | μΑ    |

| Voltage Range for Input Current Regulation (ILIM_HIZ Pin) | V <sub>IREG_DPM_RNG_ILIM</sub> |                                                                      |                                                   | 1.15 |      | 4     | V     |

|                                                           |                                |                                                                      | V <sub>ILIM_HIZ</sub> = 2.6V                      | TBD  | 4023 | TBD   |       |

| Input Current Regulation Accuracy on ILIM HIZ Pin with    |                                | V <sub>ILIM HIZ</sub> = 1V + 40 ×                                    | V <sub>ILIM_HIZ</sub> = 2.2V                      | TBD  | 3024 | TBD   | mA    |

| 10mΩ ACP/ACN Series                                       | I <sub>DPM_REG_ACC_ILIM</sub>  | I <sub>DPM</sub> × R <sub>AC</sub>                                   | V <sub>ILIM_HIZ</sub> = 1.6V                      | TBD  | 1522 | TBD   |       |

| Resistor                                                  |                                |                                                                      | V <sub>ILIM_HIZ</sub> = 1.2V                      | TBD  | 524  | TBD   |       |

| ILIM_HIZ Pin Leakage Current                              | I <sub>LEAK ILIM</sub>         |                                                                      |                                                   | TBD  | 0.01 | TBD   | μA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                | SYMBOL                    | CONDITIONS                                                  | MIN | TYP    | MAX   | UNITS |

|----------------------------------------------------------|---------------------------|-------------------------------------------------------------|-----|--------|-------|-------|

| Input Voltage Regulation                                 |                           |                                                             |     |        |       |       |

| Input Voltage Regulation Range                           | $V_{IREG\_DPM\_RNG}$      | Voltage on VBUS                                             | 3.2 |        | 19.52 | V     |

|                                                          |                           | Land Welter and an electrical Co. 2000                      |     | 18607  |       | mV    |

| Input Voltage Regulation Accuracy                        |                           | InputVoltage register = 0x3C80                              | TBD |        | TBD   | %     |

|                                                          |                           |                                                             |     | 10835  |       | mV    |

|                                                          | $V_{DPM\_REG\_ACC}$       | InputVoltage register = 0x1E00                              | TBD |        | TBD   | %     |

|                                                          |                           |                                                             |     | 4465   |       | mV    |

|                                                          |                           | InputVoltage register = 0x0500                              | TBD |        | TBD   | %     |

| OTG Current Regulation                                   |                           |                                                             |     | ı      | I.    |       |

| OTG Output Current Regulation Differential Voltage Range | V <sub>IOTG_REG_RNG</sub> | V <sub>IOTG_REG</sub> = V <sub>ACP</sub> - V <sub>ACN</sub> | 0   |        | 63.5  | mV    |

| OTG Output Current Regulation                            |                           | OTGCurrent register = 0x3C00                                | TBD | 2967   | TBD   |       |

| Accuracy with 50mA LSB and 10mΩ                          | I <sub>OTG_ACC</sub>      | OTGCurrent register = 0x1E00                                | TBD | 1474   | TBD   | mA    |

| ACP/ACN Series Resistor                                  |                           | OTGCurrent register = 0x0A00                                | TBD | 478    | TBD   |       |

| OTG Voltage Regulation                                   |                           |                                                             |     |        |       |       |

| OTG Voltage Regulation Range                             | $V_{OTG\_REG\_RNG}$       | Voltage on VBUS                                             | 3   |        | 20.56 | V     |

|                                                          |                           | OTGVoltage register = 0x23F8,<br>OTG_RANGE_LOW = 0          |     | 19.621 |       | V     |

|                                                          |                           |                                                             | TBD |        | TBD   | %     |

| OTC Valte as Describetion Assumes                        | 1/                        | OTGVoltage register = 0x1710,                               |     | 11.779 |       | V     |

| OTG Voltage Regulation Accuracy                          | V <sub>OTG_REG_ACC</sub>  | OTG_RANGE_LOW = 1                                           | TBD |        | TBD   | %     |

|                                                          |                           | OTGVoltage register = 0x099CH,                              |     | 4.928  |       | V     |

|                                                          |                           | OTG_RANGE_LOW = 1                                           | TBD |        | TBD   | %     |

| Reference and Buffer                                     |                           |                                                             |     |        |       |       |

| REGN Regulator                                           |                           |                                                             |     |        |       |       |

| REGN Regulator Voltage<br>(0mA to 60mA)                  | V <sub>REGN_REG</sub>     | V <sub>VBUS</sub> = 10V                                     | TBD | 6.15   | TBD   | V     |

| REGN Voltage in Drop Out Mode                            | V <sub>DROPOUT</sub>      | V <sub>VBUS</sub> = 5V, I <sub>LOAD</sub> = 20mA            | TBD | 4.8    | TBD   | V     |

| REGN Current Limit when Converter is Enabled             | REGN_LIM_Charging         | V <sub>VBUS</sub> = 10V, force V <sub>REGN</sub> = 4V       | TBD | 106    |       | mA    |

| REGN Output Capacitor Required for Stability             | C <sub>REGN</sub>         | I <sub>LOAD</sub> = 100μA to 50mA                           | 2.2 |        |       | μF    |

| VDDA Input Capacitor Required for Stability              | $C_{VDDA}$                | $I_{LOAD} = 100 \mu A \text{ to } 50 \text{mA}$             | 1   |        |       | μF    |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                                                                                                                                                                                                        | SYMBOL                             | CONDIT                                                                | TIONS                                                                  | MIN | TYP     | MAX | UNITS |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----|---------|-----|-------|--|

| Quiescent Current                                                                                                                                                                                                                                                |                                    |                                                                       |                                                                        |     |         |     |       |  |

|                                                                                                                                                                                                                                                                  |                                    | V <sub>BAT</sub> = 18V, EN_LWPWR = 1, in low power mode               |                                                                        |     | 21.13   | TBD |       |  |

| System Powered by Battery, BATFET                                                                                                                                                                                                                                |                                    | V <sub>BAT</sub> = 18V, EN_LWPV<br>EN_PROCHOT_LPW                     |                                                                        |     | 186.41  | TBD |       |  |

| on, I <sub>SRN</sub> + I <sub>SRP</sub> + I <sub>SW2</sub> + I <sub>BTST2</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> + I <sub>VBUS</sub> + I <sub>VSYS</sub>                                                            | I <sub>BAT_BATFET_ON</sub>         | V <sub>BAT</sub> = 18V, EN_LWPV<br>EN_PSYS = 0, REGN                  |                                                                        |     | 1146    | TBD | μΑ    |  |

|                                                                                                                                                                                                                                                                  |                                    |                                                                       | V <sub>BAT</sub> = 18V, EN_LWPWR = 0,<br>EN_PSYS = 1, REGN on, EN_PSYS |     | 1260    | TBD |       |  |

| Input Current during PFM in Buck Mode, No Load, $I_{VBUS} + I_{ACP} + I_{ACN} + I_{VSYS} + I_{SRP} + I_{SRN} + I_{SW1} + I_{BTST1} + I_{SW2} + I_{BTST2}$                                                                                                        | I <sub>AC_SW_LIGHT_buck</sub>      | V <sub>IN</sub> = 20V, V <sub>BAT</sub> = 12.6'<br>EN_OOA = 0, MOSFE  |                                                                        |     | 2.5     |     | mA    |  |

| Input Current during PFM in Boost Mode, No Load, $I_{VBUS} + I_{ACP} + I_{ACN} + I_{VSYS} + I_{SRP} + I_{SRN} + I_{SW1} + I_{BTST1} + I_{SW2} + I_{BTST2}$                                                                                                       | I <sub>AC_SW_LIGHT_boost</sub>     | V <sub>IN</sub> = 5V, V <sub>BAT</sub> = 8.4V, 2<br>EN_OOA = 0, MOSFE |                                                                        |     | 6.7     |     | mA    |  |

| Input Current during PFM in Buck<br>Boost Mode, No Load, I <sub>VBUS</sub> + I <sub>ACP</sub> +<br>I <sub>ACN</sub> + I <sub>VSYS</sub> + I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>SW1</sub> + I <sub>BTST1</sub><br>+ I <sub>SW2</sub> + I <sub>BTST2</sub> | I <sub>AC_SW_LIGHT_buckboost</sub> | V <sub>IN</sub> = 12V, V <sub>BAT</sub> = 12V,<br>EN_OOA = 0, MOSFE   |                                                                        |     | 3.3     |     | mA    |  |

| Quiescent Current during PFM in                                                                                                                                                                                                                                  |                                    | $V_{BAT} = 8.4V,$                                                     | V <sub>VBUS</sub> = 5V                                                 |     | 3.3     |     |       |  |

| OTG Mode, $I_{VBUS} + I_{ACP} + I_{ACN} + I_{VSYS} +$                                                                                                                                                                                                            | I <sub>OTG_STANDBY</sub>           | 800kHz switching frequency,                                           | V <sub>VBUS</sub> = 12V                                                | •   | 3.6     |     | mA    |  |

| $I_{SRP} + I_{SRN} + I_{SW1} + I_{BTST1} + I_{SW2} + I_{BTST2}$                                                                                                                                                                                                  |                                    | MOSFET Qg = 4nC                                                       | V <sub>VBUS</sub> = 20V                                                |     | 4       |     |       |  |

| Input Common Mode Range                                                                                                                                                                                                                                          | V <sub>ACP/N_OP</sub>              | Voltage on ACP/ACN                                                    |                                                                        | 3.8 |         | 24  | V     |  |

| IADPT Output Clamp Voltage                                                                                                                                                                                                                                       | V <sub>IADPT_CLAMP</sub>           |                                                                       |                                                                        | TBD | 3.18    | TBD | V     |  |

| IADPT Output Current                                                                                                                                                                                                                                             | I <sub>IADPT</sub>                 |                                                                       |                                                                        |     |         | 1   | mA    |  |

| Input Current Sensing Gain                                                                                                                                                                                                                                       |                                    | V A                                                                   | IADPT_GAIN = 0                                                         |     | 20      |     | V/V   |  |

| input Guirent Sensing Gain                                                                                                                                                                                                                                       | $A_{IADPT}$                        | V <sub>IADPT</sub> /V <sub>(ACP-ACN)</sub>                            | IADPT_GAIN = 1                                                         |     | 40      |     | V/V   |  |

|                                                                                                                                                                                                                                                                  |                                    | $V_{(ACP-ACN)} = 40.96 \text{mV}$                                     |                                                                        | TBD | 0.74    | TBD |       |  |

| Input Current Monitor Accuracy                                                                                                                                                                                                                                   | V                                  | V <sub>(ACP-ACN)</sub> = 20.48mV                                      |                                                                        | TBD | 1.39    | TBD | %     |  |

| input current Monitor Accuracy                                                                                                                                                                                                                                   | V <sub>IADPT_ACC</sub>             | V <sub>(ACP-ACN)</sub> =10.24mV                                       |                                                                        | TBD | 2.52    | TBD | 70    |  |

|                                                                                                                                                                                                                                                                  |                                    | $V_{(ACP-ACN)} = 5.12mV$                                              |                                                                        | TBD | 5.23    | TBD |       |  |

| Maximum Capacitance on IADPT Pin                                                                                                                                                                                                                                 | C <sub>IADPT_MAX</sub>             |                                                                       |                                                                        |     |         | 100 | pF    |  |

| Battery Common Mode Range                                                                                                                                                                                                                                        | V <sub>SRP/N_OP</sub>              | Voltage on SRP/SRN                                                    |                                                                        | 2.5 |         | 18  | V     |  |

| IBAT Output Clamp Voltage                                                                                                                                                                                                                                        | V <sub>IBAT_CLAMP</sub>            |                                                                       |                                                                        | TBD | 3.28    | TBD | V     |  |

| IBAT Output Current                                                                                                                                                                                                                                              | I <sub>IBAT</sub>                  |                                                                       |                                                                        |     |         | 1   | mA    |  |

| Charge and Discharge Current<br>Sensing Gain on IBAT Pin                                                                                                                                                                                                         | A <sub>IBAT</sub>                  | V <sub>IBAT</sub> /V <sub>(SRN-SRP)</sub>                             | IBAT_GAIN = 0 IBAT_GAIN = 1                                            |     | 8<br>16 |     | V/V   |  |

| <del>-</del>                                                                                                                                                                                                                                                     |                                    | V <sub>(SDN SDD)</sub> = 40 96mV                                      | .5, 11_5, 1114                                                         | TBD | 1.53    | TBD |       |  |

| Channa and Diagham Orman                                                                                                                                                                                                                                         |                                    | $V_{(SRN-SRP)} = 40.96\text{mV}$ $V_{(SRN-SRP)} = 20.48\text{mV}$     |                                                                        | TBD | 2.32    | TBD | - %   |  |

| Charge and Discharge Current<br>Monitor Accuracy on IBAT Pin                                                                                                                                                                                                     | V <sub>IBAT_CHG_ACC</sub>          | $V_{(SRN-SRP)} = 20.48 \text{mV}$ $V_{(SRN-SRP)} = 10.24 \text{mV}$   |                                                                        | TBD | 3.81    | TBD |       |  |

|                                                                                                                                                                                                                                                                  |                                    | $V_{(SRN-SRP)} = 5.12mV$                                              |                                                                        | TBD | 7.24    | TBD |       |  |

| Maximum Capacitance on IBAT Pin                                                                                                                                                                                                                                  | C <sub>IBAT_MAX</sub>              | - (5144-514)                                                          |                                                                        |     | 1.2.    | 100 | pF    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAME                                 | TER             | SYMBOL                        | CONDITIONS                                                                                  | MIN | TYP   | MAX | UNITS |

|----------------------------------------|-----------------|-------------------------------|---------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| System Power Ser                       | nse Amplifier   |                               |                                                                                             |     |       |     |       |

| PSYS Output Voltag                     | ge Range        | $V_{PSYS}$                    |                                                                                             | 0   |       | 3.3 | V     |

| PSYS Output Curre                      | ent             | I <sub>PSYS</sub>             |                                                                                             | 0   |       | 160 | μΑ    |

| PSYS System Gain                       |                 | A <sub>PSYS</sub>             | V <sub>PSYS</sub> /(P <sub>IN</sub> +P <sub>BAT</sub> ), PSYS_RATIO = 1                     |     | 1     |     | μΑ/W  |

| DSVS Cain Acquire                      |                 | V                             | Adapter only with system power = 19.5V/45W, PSYS_RATIO = 1, T <sub>A</sub> = -40°C to +85°C | TBD | 1.7   | TBD | 0/    |

| PSYS Gain Accurac                      | су              | V <sub>PSYS_ACC</sub>         | Battery only with system power = 11V/44W, PSYS_RATIO = 1, T <sub>A</sub> = -40°C to +85°C   | TBD | 0.27  | TBD | %     |

| PSYS Clamp Voltag                      | ge              | $V_{PSYS\_CLAMP}$             |                                                                                             | TBD | 3.3   | TBD | V     |

| Comparator                             |                 |                               |                                                                                             |     |       |     |       |

| VBUS Under-Volta                       | •               | mparator                      |                                                                                             |     |       |     |       |

| VBUS Under-Voltage Threshold           |                 | $V_{VBUS\_UVLOZ}$             | VBUS rising                                                                                 | TBD | 2.55  | TBD | V     |

| VBUS Under-Voltage Threshold           | ge Falling      | $V_{VBUS\_UVLO}$              | VBUS falling                                                                                | TBD | 2.4   | TBD | V     |

| VBUS Under-Voltag                      | -               | $V_{\text{VBUS\_UVLO\_HYST}}$ |                                                                                             |     | 150   |     | mV    |

| VBUS Converter Er<br>Threshold         | nable Rising    | V <sub>VBUS_CONVEN</sub>      | VBUS rising                                                                                 | TBD | 3.58  | TBD | V     |

| VBUS Converter Er<br>Threshold         | nable Falling   | V <sub>VBUS_CONVENZ</sub>     | VBUS falling                                                                                | TBD | 3.21  | TBD | V     |

| VBUS Converter Er<br>Hysteresis        | nable           | Vvbus_conven_hyst             |                                                                                             |     | 377   |     | mV    |

| Battery Under-Volt                     | tage Lockout C  | omparator                     |                                                                                             |     |       |     |       |

| VBAT Under-Voltag<br>Threshold         | e Rising        | V <sub>VBAT_UVLOZ</sub>       | VSRN rising                                                                                 | TBD | 2.56  | TBD | V     |

| VBAT Under-Voltag<br>Threshold         | e Falling       | V <sub>VBAT_UVLO</sub>        | VSRN falling                                                                                | TBD | 2.41  | TBD | V     |

| VBAT Under-Voltag                      | e Hysteresis    | V <sub>VBAT_UVLO_HYST</sub>   |                                                                                             |     | 150   |     | mV    |

| VBAT OTG Enable<br>Threshold           | Rising          | V <sub>VBAT_OTGEN</sub>       | VSRN rising                                                                                 | TBD | 3.57  | TBD | V     |

| VBAT OTG Enable<br>Threshold           | Falling         | V <sub>VBAT_OTGENZ</sub>      | VSRN falling                                                                                | TBD | 2.36  | TBD | V     |

| VBAT OTG Enable                        | Hysteresis      | V <sub>VBAT_OTGEN_HYST</sub>  |                                                                                             |     | 1208  |     | mV    |

| VBUS Under-Volta                       | ge Comparator   | (OTG Mode)                    |                                                                                             | •   |       | •   | •     |

| VBUS Under-Voltage<br>Threshold        | ge Falling      | $V_{VBUS\_OTG\_UV}$           | As percentage of OTGVoltage register                                                        |     | 0.85  |     |       |

| VBUS Time Under-<br>Deglitch           | Voltage         | t <sub>VBUS_OTG_UV</sub>      |                                                                                             |     | 7     |     | ms    |

| VBUS Over-Voltag                       | e Comparator    | (OTG Mode)                    |                                                                                             |     |       |     |       |

| VBUS Over-Voltage<br>Threshold         | Rising          | V <sub>VBUS_OTG_OV</sub>      | As percentage of OTGVoltage register                                                        |     | 1.1   |     |       |

| VBUS Time Over-V                       | oltage Deglitch | t <sub>VBUS_OTG_OV</sub>      |                                                                                             |     | 10    |     | ms    |

| Pre-Charge to Fas                      | -               | ition                         |                                                                                             |     |       |     |       |

| LDO Mode to Fast<br>Charge Mode        | VSRN Rising     | V <sub>BAT_SYSMIN_RISE</sub>  | As percentage of MinSystemVoltage register                                                  | TBD | 99.51 | TBD | %     |

| Threshold                              | VSRN Falling    | V <sub>BAT_SYSMIN_FALL</sub>  | As percentage of will system voltage register                                               |     | 97.88 |     | /0    |

| Fast Charge Mode<br>Threshold Hysteres |                 | V <sub>BAT_SYSMIN_HYST</sub>  | As percentage of MinSystemVoltage register                                                  |     | 1.63  |     | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                               | SYMBOL                      | CONDITIONS                                     |                  | MIN | TYP   | MAX | UNITS |

|-------------------------------------------------------------------------|-----------------------------|------------------------------------------------|------------------|-----|-------|-----|-------|

| Battery LOWV Comparator (Pre-Cha                                        | rge to Fast Ch              | arge Threshold for 1-Cell)                     |                  |     |       |     |       |

| BATLOWV Falling Threshold                                               | $V_{BATLV\_FALL}$           | 1-cell                                         |                  |     | 2.8   |     | V     |

| BATLOWV Rising Threshold                                                | $V_{BATLV\_RISE}$           |                                                |                  |     | 3     |     | V     |

| BATLOWV Hysteresis                                                      | V <sub>BATLV_HYST</sub>     |                                                |                  |     | 193   |     | mV    |

| Input Over-Voltage Comparator (AC                                       | OVP)                        |                                                |                  |     | •     |     |       |

| VBUS Over-Voltage Rising Threshold                                      | V <sub>ACOV_RISE</sub>      | VBUS rising                                    |                  | TBD | 25.8  | TBD | V     |

| VBUS Over-Voltage Falling Threshold                                     | V <sub>ACOV_FALL</sub>      | VBUS falling                                   |                  | TBD | 23.9  | TBD | V     |

| VBUS Over-Voltage Hysteresis                                            | V <sub>ACOV_HYST</sub>      |                                                |                  |     | 1.9   |     | V     |

| VBUS Deglitch Over-Voltage Rising                                       | t <sub>ACOV_RISE_DEG</sub>  | VBUS converter rising to stop of               | converter        |     | 100   |     | μs    |

| VBUS Deglitch Over-Voltage Falling                                      | tacov_fall_deg              | VBUS converter falling to start                | converter        |     | 1     |     | ms    |

| Input Over-Current Comparator (AC                                       | OC)                         |                                                |                  |     | •     |     |       |

| ACP to ACN Rising Threshold,<br>w.r.t. ILIM2 in ILIM2_VTH[4:0] Bits     | V <sub>ACOC</sub>           | Voltage across input sense res<br>ACOC_VTH = 1 | istor rising,    | TBD | 2     | TBD |       |

| Measure between ACP and ACN                                             | V <sub>ACOC_FLOOR</sub>     | Set IDPM to minimum                            |                  | TBD | 50    | TBD | mV    |

| Measure between ACP and ACN                                             | V <sub>ACOC_CEILING</sub>   | Set IDPM to maximum                            |                  | TBD | 180   | TBD | mV    |

| Rising Deglitch Time                                                    | tacoc_deg_rise              | Deglitch time to trigger ACOC                  |                  |     | 250   |     | μs    |