# DRV89xx-Q1 Automotive Multi-Channel Half-Bridge Drivers with Advanced Diagnostics

#### 1 Features

- AEC-Q100 qualified for automotive applications

- 4, 6, 8, 10 and 12 half-bridge outputs

- 4.5-V to 32-V operating voltage

- 40-V absolute maximum voltage

- 1-A RMS current for each output

- 6-A maximum current for paralleled outputs

- Low-power sleep mode (1.5-µA)

- Supports 3.3-V and 5-V logic inputs

- SPI for configuration and diagnostics

- 5-MHz, 16-Bit SPI communication

- Daisy chain functionality

- PWM generators programmable over SPI

- Individual half-bridge PWM operation

- Configurable for high-side, low-side, and Hbridge load driving

- Supports 8-bit duty cycle resolution

- Integrated protection features with per channel detailed diagnostics over SPI

- nFAULT pin output

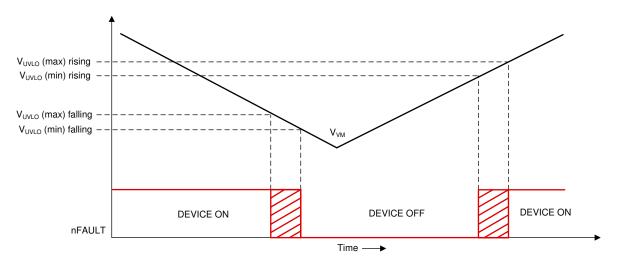

- VM undervoltage lockout (UVLO)

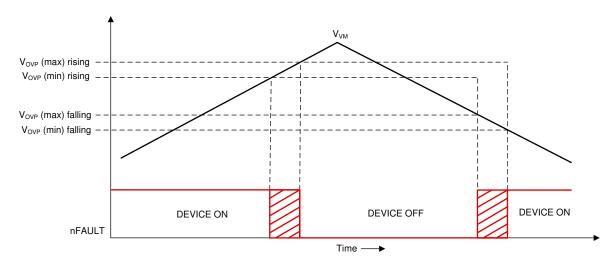

- VM overvoltage protection (OVP)

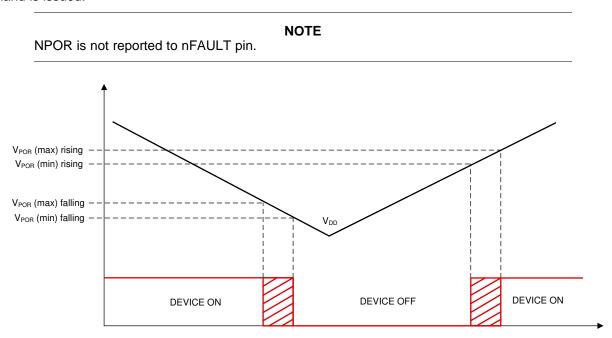

- Logic supply power on reset (POR)

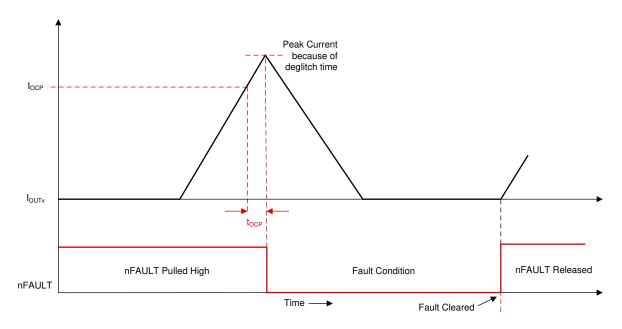

- Overcurrent protection (OCP)

- Enhanced open load detection (OLD)

- Thermal warning and shutdown (OTW/OTSD)

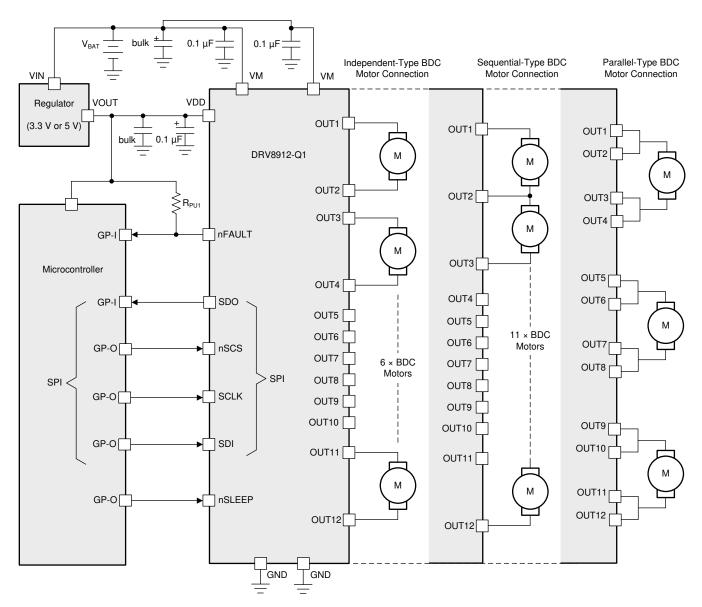

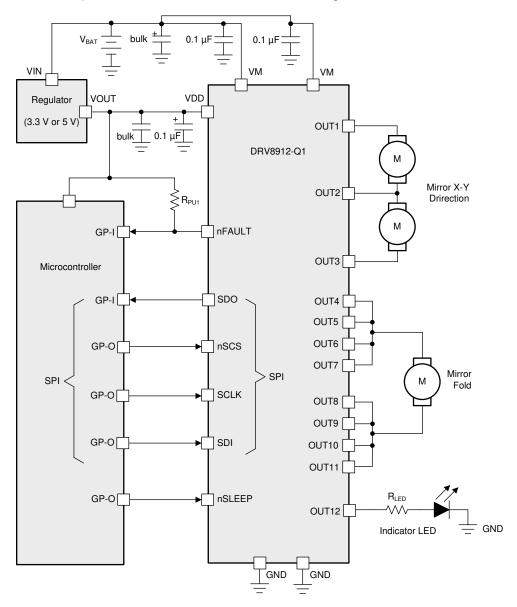

### 2 Applications

- HVAC flap DC motors

- Side mirror adjustment and mirror fold

- LED applications

- Multiple brushed DC motors and solenoids

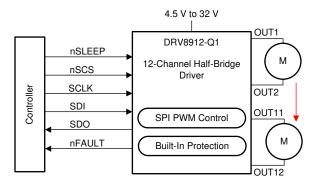

#### 3 Description

The DRV89xx-Q1 is a pin-to-pin compatible family of integrated multi-channel half-bridge drivers with 4 to 12 half-bridges. The device family features low on-state resistance ( $R_{\rm DS(ON)}$ ) for improved thermal performance during high-current operation.

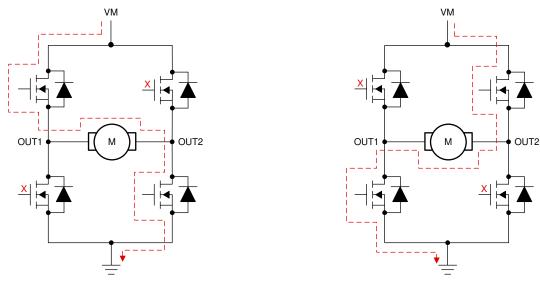

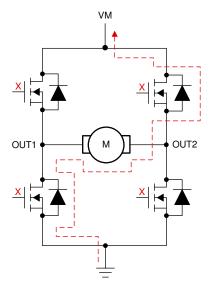

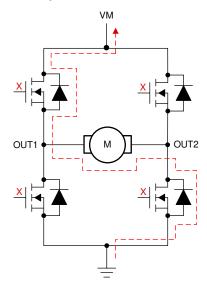

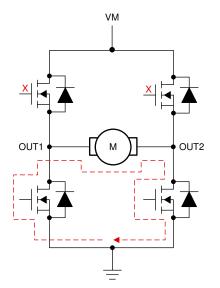

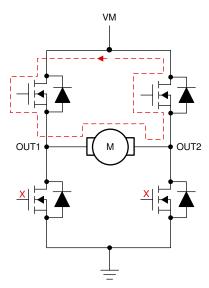

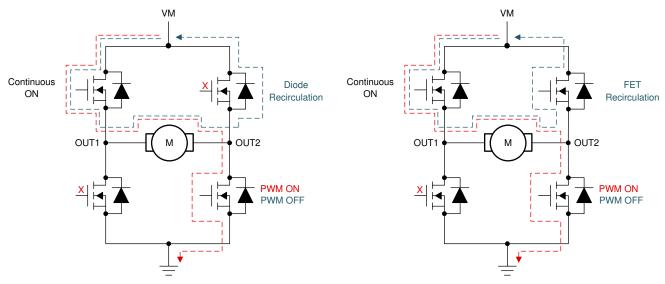

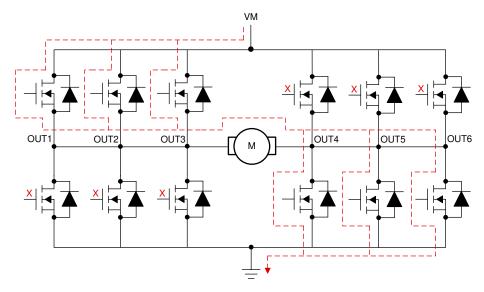

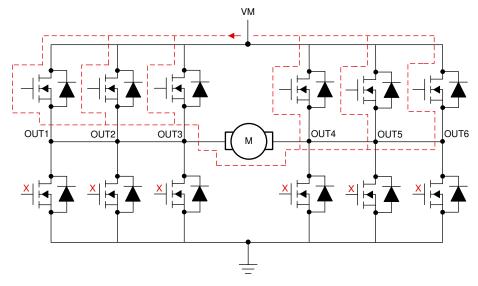

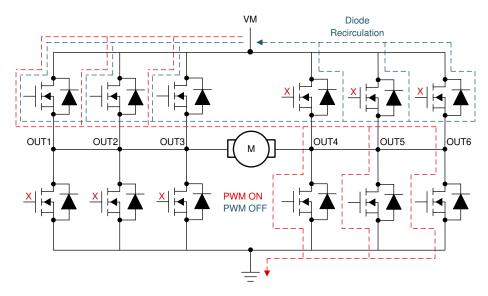

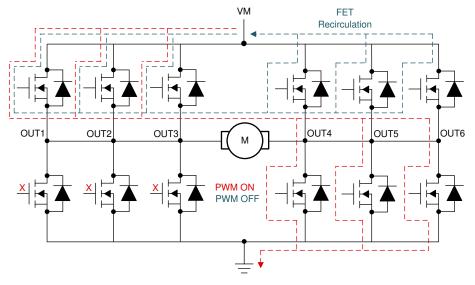

These devices can drive brushed-DC (BDC) motors or stepper motors in independent, sequential, or parallel mode. The half-bridges are fully controllable to achieve a forward, reverse, coasting and braking operation of motor.

These devices feature standard 16-bit, 5-MHz serial peripheral interface (SPI) with daisy chain capability for complete configuration and detailed diagnostics. Depending on the device, four or eight programmable PWM generators are integrated to allow for current limiting during motor operation or LED dimming control.

The device includes numerous protection and diagnostic features including an nFAULT pin to alert the system when a fault occurs. The device features a low-current open load detection (OLD) mode to detect open-load conditions when the nominal load current is small and a passive OLD mode for offline OLD. The device is also fully-protected from short-circuit, undervoltage, and over-temperature conditions.

View our full portfolio of brushed motor drivers on ti.com.

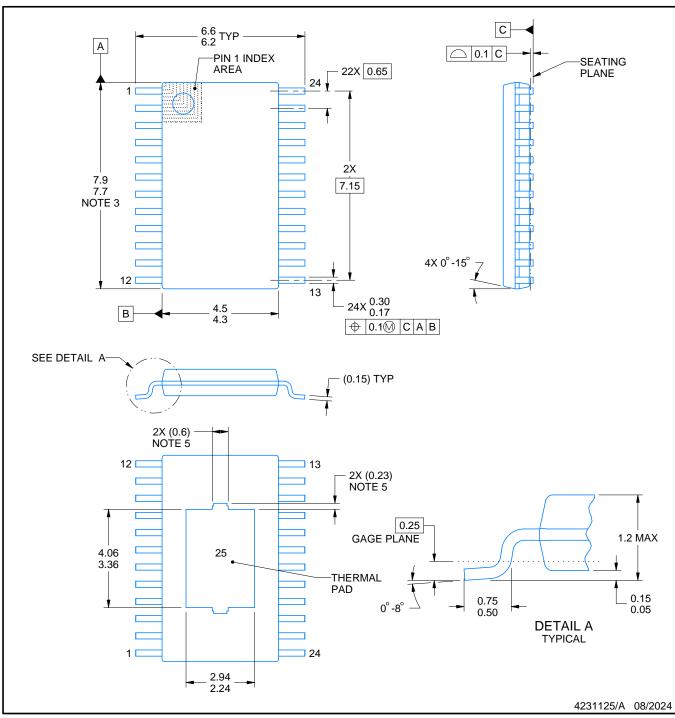

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |

|-------------|-------------|-------------------|

| DRV8912-Q1  |             |                   |

| DRV8910-Q1  |             |                   |

| DRV8908-Q1  | HTSSOP (24) | 7.80 mm × 4.40 mm |

| DRV8906-Q1  |             |                   |

| DRV8904-Q1  |             |                   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

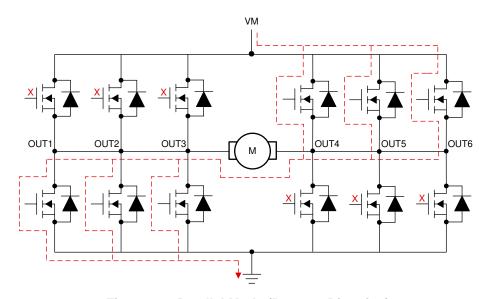

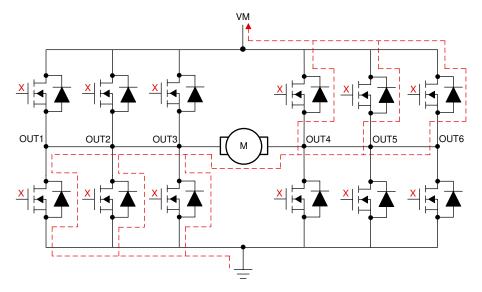

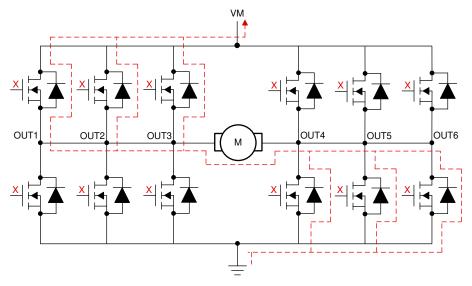

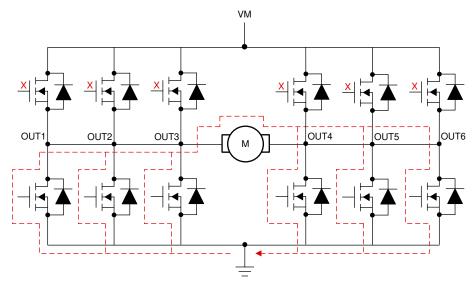

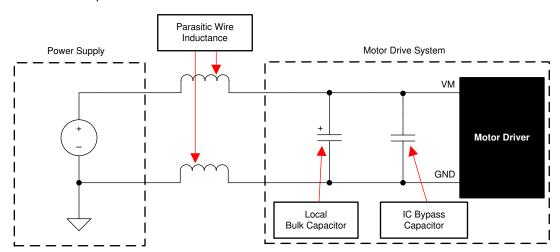

#### Simplified Schematic

## **Table of Contents**

| 1 | Features 1                           |    | 8.6 Register Map                                     | 63  |

|---|--------------------------------------|----|------------------------------------------------------|-----|

| 2 | Applications 1                       | 9  | Application and Implementation                       | 129 |

| 3 | Description 1                        |    | 9.1 Application Information                          | 129 |

| 4 | Revision History2                    |    | 9.2 Typical Application                              | 130 |

| 5 | Device Comparison Table              |    | 9.3 Thermal Application                              | 135 |

| 6 | Pin Configuration and Functions 4    | 10 | Power Supply Recommendations                         | 141 |

| 7 | Specifications                       |    | 10.1 Bulk Capacitance Sizing                         | 141 |

| ′ | 7.1 Absolute Maximum Ratings         | 11 | Layout                                               |     |

|   | 7.2 ESD Ratings                      |    | 11.1 Layout Guidelines                               | 142 |

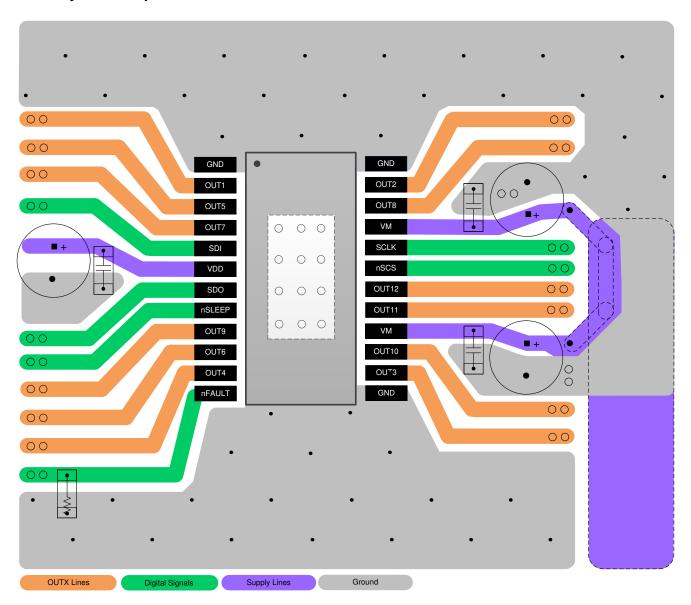

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example                                  | 142 |

|   | 7.4 Thermal Information              | 12 | Device and Documentation Support                     |     |

|   | 7.5 Electrical Characteristics       |    | 12.1 Documentation Support                           |     |

|   | 7.6 Timing Requirements              |    | 12.2 Related Links                                   |     |

|   | 7.7 Typical Characteristics          |    | 12.3 Receiving Notification of Documentation Updates | 143 |

| 8 | Detailed Description25               |    | 12.4 Community Resources                             |     |

|   | 8.1 Overview                         |    | 12.5 Trademarks                                      |     |

|   | 8.2 Functional Block Diagram         |    | 12.6 Electrostatic Discharge Caution                 |     |

|   | 8.3 Feature Description              |    | 12.7 Glossary                                        |     |

|   | 8.4 Device Functional Modes 57       | 13 | Mechanical, Packaging, and Orderable                 |     |

|   | 8.5 Programming                      |    | Information                                          | 143 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (December 2019) to Revision C                                                                                         | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Changed Test Conditions for t <sub>PD</sub>                                                                                                   | 16   |

| Added MIN/MAX specs for f <sub>PWM</sub>                                                                                                      | 16   |

| Added MIN/MAX specs for t <sub>OCP</sub>                                                                                                      | 17   |

| <ul> <li>Changed I<sub>OL_VM/GND</sub> V<sub>OL_VM/GND</sub> specs based on production test data for DRV8908/06/04 product release</li> </ul> | 17   |

| Changed Figure 2 and Figure 3 with new data                                                                                                   | 20   |

| Added Figure 61 and Figure 62                                                                                                                 | 47   |

| Changes from Revision A (December 2019) to Revision B                                                                                         | Page |

| Changed device status to Production Mixed                                                                                                     | 1    |

| Changes from Original (September 2019) to Revision A                                                                                          | Page |

| Changed device status to Production Data                                                                                                      | 1    |

# 5 Device Comparison Table

| DEVICE     | NUMBER OF HALF-<br>BRIDGES | NUMBER OF PWM<br>GENERATORS | OPEN-LOAD DETECTION SCHEMES                         | LINK TO REGISTER MAP |

|------------|----------------------------|-----------------------------|-----------------------------------------------------|----------------------|

| DRV8912-Q1 | 12                         | 4                           | Active OLD, Low-Current                             | Table 17             |

| DRV8910-Q1 | 10                         | 4                           | Active OLD, Negative-Current Active OLD             | Table 18             |

| DRV8908-Q1 | 8                          | 8                           | Passive OLD, Active OLD,                            | Table 50             |

| DRV8906-Q1 | 6                          | 8                           | Low-Current Active OLD, Negative-Current Active OLD | Table 51             |

| DRV8904-Q1 | 4                          | 8                           |                                                     | Table 52             |

## 6 Pin Configuration and Functions

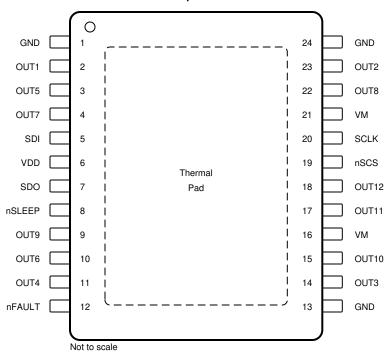

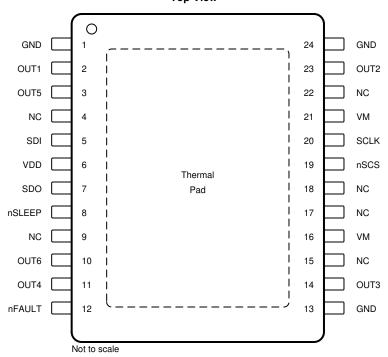

DRV8912-Q1 PWP Package 24-Pin HTSSOP Package With Exposed Thermal Pad Top View

#### Pin Functions—DRV8912-Q1

| PIN    |     | TYPE | DECORPTION                                                                                                               |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | ITPE | DESCRIPTION                                                                                                              |

| GND    | 13  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                           |

| GND    | 24  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                           |

| GND    | 1   | PWR  | Device power ground. Connect the GND pin to the system ground.                                                           |

| nFAULT | 12  | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor. |

| nSCS   | 19  | 1    | Serial chip select. A logic low on this pin enables serial interface communication. Internal pull-up.                    |

| nSLEEP | 8   | 1    | Driver enable pin. When this pin is logic low the device goes to a low-power sleep mode. Internal pull-down.             |

| OUT1   | 2   | 0    | Half-bridge 1 output                                                                                                     |

| OUT2   | 23  | 0    | Half-bridge 2 output                                                                                                     |

| OUT3   | 14  | 0    | Half-bridge 3 output                                                                                                     |

| OUT4   | 11  | 0    | Half-bridge 4 output                                                                                                     |

| OUT5   | 3   | 0    | Half-bridge 5 output                                                                                                     |

| OUT6   | 10  | 0    | Half-bridge 6 output                                                                                                     |

| OUT7   | 4   | 0    | Half-bridge 7 output                                                                                                     |

| OUT8   | 22  | 0    | Half-bridge 8 output                                                                                                     |

| OUT9   | 9   | 0    | Half-bridge 9 output                                                                                                     |

| OUT10  | 15  | 0    | Half-bridge 10 output                                                                                                    |

| OUT11  | 17  | 0    | Half-bridge 11 output                                                                                                    |

| OUT12  | 18  | 0    | Half-bridge 12 output                                                                                                    |

## Pin Functions—DRV8912-Q1 (continued)

| PIN  |     | TYPE | DECODIDATION                                                                                                                                                                                                                             |  |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | ITPE | DESCRIPTION                                                                                                                                                                                                                              |  |

| SCLK | 20  | I    | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pull-down.                                                                                                |  |

| SDI  | 5   | 1    | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pull-down.                                                                                                                                             |  |

| SDO  | 7   | 0    | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                                                                                                                                              |  |

| VDD  | 6   | PWR  | Logic power supply input. Connect a X5R or X7R, 0.1- $\mu$ F, VDD-rated ceramic capacitor and greater than or equal to 1- $\mu$ F bulk capacitance between the VDD and GND pins.                                                         |  |

| VM   | 16  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

| VM   | 21  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

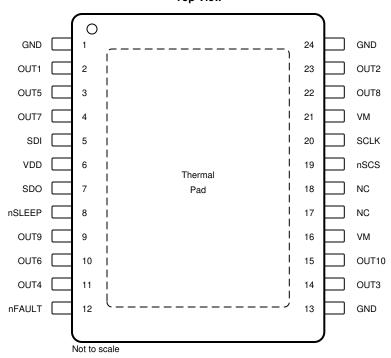

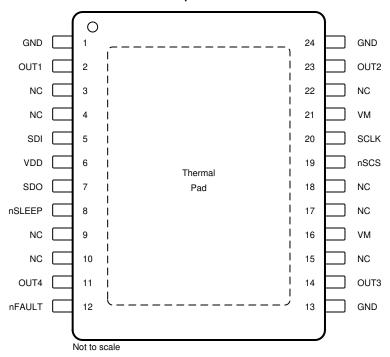

#### DRV8910-Q1 PWP Package 24-Pin HTSSOP Package With Exposed Thermal Pad Top View

### Pin Functions—DRV8910-Q1

| PIN    |     | TYPE | DECORPORTION                                                                                                                              |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | IIFE | DESCRIPTION                                                                                                                               |

| GND    | 13  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 24  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 1   | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| NC     | 17  | _    | Not connected                                                                                                                             |

| NC     | 18  | _    | Not connected                                                                                                                             |

| nFAULT | 12  | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor.                  |

| nSCS   | 19  | 1    | Serial chip select. A logic low on this pin enables serial interface communication. Internal pull-up.                                     |

| nSLEEP | 8   | I    | Driver enable pin. When this pin is logic low the device goes to a low-power sleep mode. Internal pull-down.                              |

| OUT1   | 2   | 0    | Half-bridge 1 output                                                                                                                      |

| OUT2   | 23  | 0    | Half-bridge 2 output                                                                                                                      |

| OUT3   | 14  | 0    | Half-bridge 3 output                                                                                                                      |

| OUT4   | 11  | 0    | Half-bridge 4 output                                                                                                                      |

| OUT5   | 3   | 0    | Half-bridge 5 output                                                                                                                      |

| OUT6   | 10  | 0    | Half-bridge 6 output                                                                                                                      |

| OUT7   | 4   | 0    | Half-bridge 7 output                                                                                                                      |

| OUT8   | 22  | 0    | Half-bridge 8 output                                                                                                                      |

| OUT9   | 9   | 0    | Half-bridge 9 output                                                                                                                      |

| OUT10  | 15  | 0    | Half-bridge 10 output                                                                                                                     |

| SCLK   | 20  | I    | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pull-down. |

| SDI    | 5   | I    | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pull-down.                                              |

## Pin Functions—DRV8910-Q1 (continued)

| PIN  |     | TVDE | DECORPTION                                                                                                                                                                                                                               |  |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                              |  |

| SDO  | 7   | 0    | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                                                                                                                                              |  |

| VDD  | 6   | PWR  | Logic power supply input. Connect a X5R or X7R, 0.1- $\mu$ F, VDD-rated ceramic capacitor and greater than or equal to 1- $\mu$ F bulk capacitance between the VDD and GND pins.                                                         |  |

| VM   | 16  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

| VM   | 21  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

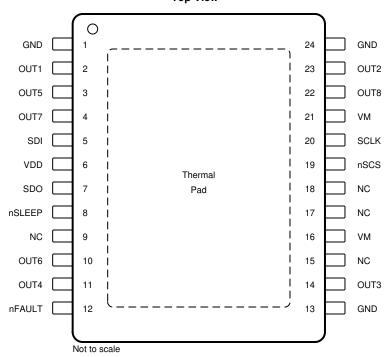

#### DRV8908-Q1 PWP Package 24-Pin HTSSOP Package With Exposed Thermal Pad Top View

#### Pin Functions—DRV8908-Q1

| PIN    |     | TVDE | DESCRIPTION                                                                                                                               |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPE | DESCRIPTION                                                                                                                               |

| GND    | 13  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 24  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 1   | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| NC     | 9   | _    | Not connected                                                                                                                             |

| NC     | 15  | _    | Not connected                                                                                                                             |

| NC     | 17  | _    | Not connected                                                                                                                             |

| NC     | 18  | _    | Not connected                                                                                                                             |

| nFAULT | 12  | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor.                  |

| nSCS   | 19  | 1    | Serial chip select. A logic low on this pin enables serial interface communication. Internal pull-up.                                     |

| nSLEEP | 8   | I    | Driver enable pin. When this pin is logic low the device goes to a low-power sleep mode. Internal pull-down.                              |

| OUT1   | 2   | 0    | Half-bridge 1 output                                                                                                                      |

| OUT2   | 23  | 0    | Half-bridge 2 output                                                                                                                      |

| OUT3   | 14  | 0    | Half-bridge 3 output                                                                                                                      |

| OUT4   | 11  | 0    | Half-bridge 4 output                                                                                                                      |

| OUT5   | 3   | 0    | Half-bridge 5 output                                                                                                                      |

| OUT6   | 10  | 0    | Half-bridge 6 output                                                                                                                      |

| OUT7   | 4   | 0    | Half-bridge 7 output                                                                                                                      |

| OUT8   | 22  | 0    | Half-bridge 8 output                                                                                                                      |

| SCLK   | 20  | I    | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pull-down. |

| SDI    | 5   | I    | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pull-down.                                              |

## Pin Functions—DRV8908-Q1 (continued)

| PIN  |     | TVDE | DECORPTION                                                                                                                                                                                                                               |  |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                              |  |

| SDO  | 7   | 0    | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                                                                                                                                              |  |

| VDD  | 6   | PWR  | Logic power supply input. Connect a X5R or X7R, 0.1- $\mu$ F, VDD-rated ceramic capacitor and greater than or equal to 1- $\mu$ F bulk capacitance between the VDD and GND pins.                                                         |  |

| VM   | 16  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

| VM   | 21  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

#### DRV8906-Q1 PWP Package 24-Pin HTSSOP Package With Exposed Thermal Pad Top View

#### Pin Functions—DRV8906-Q1

| PIN    |     | TYPE | DECORPTION                                                                                                                                |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | IIFE | DESCRIPTION                                                                                                                               |

| GND    | 13  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 24  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 1   | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| NC     | 4   | _    | Not connected                                                                                                                             |

| NC     | 9   | _    | Not connected                                                                                                                             |

| NC     | 15  | _    | Not connected                                                                                                                             |

| NC     | 17  | _    | Not connected                                                                                                                             |

| NC     | 18  | _    | Not connected                                                                                                                             |

| NC     | 22  | _    | Not connected                                                                                                                             |

| nFAULT | 12  | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor.                  |

| nSCS   | 19  | I    | Serial chip select. A logic low on this pin enables serial interface communication. Internal pull-up.                                     |

| nSLEEP | 8   | I    | Driver enable pin. When this pin is logic low the device goes to a low-power sleep mode. Internal pull-down.                              |

| OUT1   | 2   | 0    | Half-bridge 1 output                                                                                                                      |

| OUT2   | 23  | 0    | Half-bridge 2 output                                                                                                                      |

| OUT3   | 14  | 0    | Half-bridge 3 output                                                                                                                      |

| OUT4   | 11  | 0    | Half-bridge 4 output                                                                                                                      |

| OUT5   | 3   | 0    | Half-bridge 5 output                                                                                                                      |

| OUT6   | 10  | 0    | Half-bridge 6 output                                                                                                                      |

| SCLK   | 20  | - 1  | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pull-down. |

| SDI    | 5   | I    | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pull-down.                                              |

## Pin Functions—DRV8906-Q1 (continued)

| PIN  |     | TVDE | DECODINE                                                                                                                                                                                                                                 |  |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                              |  |

| SDO  | 7   | 0    | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                                                                                                                                              |  |

| VDD  | 6   | PWR  | Logic power supply input. Connect a X5R or X7R, 0.1- $\mu$ F, VDD-rated ceramic capacitor and greater than or equal to 1- $\mu$ F bulk capacitance between the VDD and GND pins.                                                         |  |

| VM   | 16  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

| VM   | 21  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |  |

#### DRV8904-Q1 PWP Package 24-Pin HTSSOP Package With Exposed Thermal Pad Top View

### Pin Functions—DRV8904-Q1

| F      | PIN | TYPE | DESCRIPTION                                                                                                                               |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | ITPE | DESCRIPTION                                                                                                                               |

| GND    | 13  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 24  | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| GND    | 1   | PWR  | Device power ground. Connect the GND pin to the system ground.                                                                            |

| NC     | 3   | _    | Not connected                                                                                                                             |

| NC     | 4   | _    | Not connected                                                                                                                             |

| NC     | 9   | _    | Not connected                                                                                                                             |

| NC     | 10  | _    | Not connected                                                                                                                             |

| NC     | 15  | _    | Not connected                                                                                                                             |

| NC     | 17  | _    | Not connected                                                                                                                             |

| NC     | 18  | _    | Not connected                                                                                                                             |

| NC     | 22  | _    | Not connected                                                                                                                             |

| nFAULT | 12  | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor.                  |

| nSCS   | 19  | I    | Serial chip select. A logic low on this pin enables serial interface communication. Internal pull-up.                                     |

| nSLEEP | 8   | I    | Driver enable pin. When this pin is logic low the device goes to a low-power sleep mode. Internal pull-down.                              |

| OUT1   | 2   | 0    | Half-bridge 1 output                                                                                                                      |

| OUT2   | 23  | 0    | Half-bridge 2 output                                                                                                                      |

| OUT3   | 14  | 0    | Half-bridge 3 output                                                                                                                      |

| OUT4   | 11  | 0    | Half-bridge 4 output                                                                                                                      |

| SCLK   | 20  | I    | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. Internal pull-down. |

| SDI    | 5   | I    | Serial data input. Data is captured on the falling edge of the SCLK pin. Internal pull-down.                                              |

## Pin Functions—DRV8904-Q1 (continued)

|      | PIN | TVDE | DESCRIPTION                                                                                                                                                                                                                              |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                              |

| SDO  | 7   | 0    | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                                                                                                                                              |

| VDD  | 6   | PWR  | Logic power supply input. Connect a X5R or X7R, 0.1- $\mu$ F, VDD-rated ceramic capacitor and greater than or equal to 1- $\mu$ F bulk capacitance between the VDD and GND pins.                                                         |

| VM   | 16  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |

| VM   | 21  | PWR  | Main power supply input. Connect all VM pins together to the motor supply voltage. Connect a X5R or X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor and greater than or equal to 10- $\mu$ F bulk capacitance between the VM and GND pins. |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                   | MIN                   | MAX                   | UNIT |

|---------------------------------------------------|-----------------------|-----------------------|------|

| Power supply pin voltage (VM)                     | 4.5                   | 40                    | V    |

| Logic supply pin voltage (VDD)                    | -0.3                  | 5.75                  | V    |

| Output pin voltage (OUTx)                         | -0.7                  | VM + 0.7              | V    |

| Logic pin input voltage (nSCS, nSLEEP, SCLK, SDI) | -0.3                  | VDD + 0.3             | V    |

| Logic pin output voltage (nFAULT, SDO)            | -0.3                  | VDD + 0.3             | V    |

| Continuous supply current (VM pins combined)      | 0                     | 6                     | Α    |

| Peak output current drive (OUTx)                  | Internally<br>Limited | Internally<br>Limited | А    |

| Continous sink current (GND pins combined)        | 0                     | 6                     | Α    |

| Junction temperature, T <sub>J</sub>              | -40                   | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>             | -65                   | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                             |                                |                                 |                                 | VALUE | UNIT |

|---------------------------------------------|--------------------------------|---------------------------------|---------------------------------|-------|------|

| Human body mo<br>AEC Q100-002 <sup>(1</sup> | Human body model (HBM), per    | OUTx and VM pins                | ±4000                           |       |      |

|                                             | Electros de Control de la como | AEC Q100-002 <sup>(1)</sup>     | Other pins                      | ±2000 |      |

| V <sub>(ESD)</sub>                          | Electrostatic discharge        | Charged device model (CDM), per | Corner pins (1, 12, 13, and 24) | ±750  | V    |

|                                             |                                | AEC Q100-011                    | Other pins                      | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                 |                                               | MIN | NOM MAX | UNIT |

|-----------------|-----------------------------------------------|-----|---------|------|

| $V_{VM}$        | Power supply voltage (VM)                     | 4.5 | 32      | V    |

| $V_{DD}$        | Logic supply voltage (VDD)                    | 3   | 5.5     | V    |

| V <sub>IN</sub> | Logic input voltage (nSCS, nSLEEP, SCLK, SDI) | 0   | 5.5     | V    |

| V <sub>OD</sub> | Open drain pullup voltage (nFAULT)            | 0   | 5.5     | V    |

| I <sub>OD</sub> | Open drain output current (nFAULT)            | 0   | 5       | mA   |

| V <sub>OP</sub> | Push-pull pullup voltage (SDO)                | 0   | 5.5     | V    |

| I <sub>OP</sub> | Push-pull output current (SDO)                | 0   | 5       | mA   |

| T <sub>A</sub>  | Operating ambient temperature                 | -40 | 125     | °C   |

| TJ              | Operating junction temperature                | -40 | 150     | °C   |

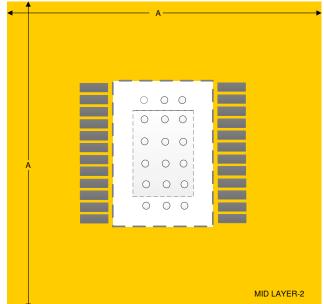

#### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                           | DRV8912-Q1<br>DRV8910-Q1 | DRV8908-Q1<br>DRV8906-Q1<br>DRV8904-Q1 | UNIT |

|-------------------------------|-------------------------------------------|--------------------------|----------------------------------------|------|

|                               |                                           | PWP (HTSSOP)             | PWP (HTSSOP)                           |      |

|                               |                                           | 24 PINS                  | 24 PINS                                |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance    | 30.2                     | 31.2                                   | °C/W |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance | 23.7                     | 25.4                                   | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance      | 10.1                     | 11.2                                   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

## **Thermal Information (continued)**

| THERMAL METRIC <sup>(1)</sup> |                                              | DRV8912-Q1<br>DRV8910-Q1 | DRV8908-Q1<br>DRV8906-Q1<br>DRV8904-Q1 | UNIT |

|-------------------------------|----------------------------------------------|--------------------------|----------------------------------------|------|

|                               |                                              | PWP (HTSSOP)             | PWP (HTSSOP)                           |      |

|                               |                                              | 24 PINS                  | 24 PINS                                |      |

| $\Psi_{\text{JT}}$            | Junction-to-top characterization parameter   | 0.3                      | 0.4                                    | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 10.0                     | 11.2                                   | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance | 2.5                      | 3.1                                    | °C/W |

### 7.5 Electrical Characteristics

at  $T_J = -40$ °C to +150°C,  $V_{VM} = 4.5$  to 32 V (Main Supply),  $V_{VDD} = 3$  to 5.5 V (Logic Supply) (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{VM} = 13.5$  V,  $V_{VDD} = 3.3$  V

|                    | PARAMETER                      | TEST CONDITIONS                                                                                                               | MIN     | TYP  | MAX      | UNIT |

|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|------|----------|------|

| POWER S            | UPPLIES (VDD, VM)              |                                                                                                                               |         |      | <u>'</u> |      |

|                    |                                | V <sub>VM</sub> = 13.5 V, nSLEEP = 0, T <sub>A</sub> = 25 °C                                                                  |         | 0.35 | 1        | μΑ   |

| $I_{VMQ}$          | VM sleep mode current          | V <sub>VM</sub> = 13.5 V, nSLEEP = 0, T <sub>A</sub> = 125 °C                                                                 |         |      | 2        | μA   |

|                    | VDD along mode assessed        | $V_{VM}$ = 13.5 V, $V_{VDD}$ = 3.3 V, nSLEEP = 0, $T_A$ = 25 °C                                                               |         | 0.01 | 0.3      | μΑ   |

| I <sub>VDDQ</sub>  | VDD sleep mode current         | $V_{VM} = 13.5 \text{ V}, V_{VDD} = 3.3 \text{ V}, \text{ nSLEEP} = 0, T_A = 125 ^{\circ}\text{C}$                            |         |      | 2        | μA   |

|                    | VM standby made current        | $V_{VM}$ = 13.5 V, nSLEEP = 1, Driver = 'OFF', $T_A$ = 25 °C                                                                  |         | 0.2  | 0.5      | mA   |

| I <sub>VMS</sub>   | VM standby mode current        | V <sub>VM</sub> = 13.5 V, nSLEEP = 1, Driver = 'OFF', T <sub>A</sub> = 125 °C                                                 |         |      | 0.5      | mA   |

|                    | VDD standby made surrent       | $V_{VM} = 13.5 \text{ V}, V_{VDD} = 3.3 \text{ V}, \text{ nSLEEP} = 1, \text{SPI} = 'OFF', T_A = 25 °C$                       |         | 0.6  | 1        | mA   |

| I <sub>VDDS</sub>  | VDD standby mode current       | $V_{VM} = 13.5 \text{ V}, V_{VDD} = 3.3 \text{ V}, \text{ nSLEEP} = 1, \text{SPI} = '\text{OFF'}, T_A = 125 ^{\circ}\text{C}$ |         |      | 1        | mA   |

|                    | VA4                            | $V_{VM}$ = 13.5 V, nSLEEP = 1, All High-<br>Side FETs = 'ON', $T_A$ = 25 °C                                                   |         | 2.6  | 5        | mA   |

| I <sub>VM</sub>    | VM operating mode current      | $V_{VM}$ = 13.5 V, nSLEEP = 1, All High-<br>Side FETs = 'ON', $T_A$ = 125 °C                                                  |         |      | 5        | mA   |

|                    | VDD                            | $V_{VM}$ = 13.5 V, $V_{VDD}$ = 3.3 V, nSLEEP = 1, All High-Side FETs = 'ON', SPI = 'ON' (5 MHz), $T_A$ = 25 °C                |         | 2.8  | 5        | mA   |

| I <sub>VDD</sub>   | VDD operating mode current     | $V_{VM}$ = 13.5 V, $V_{VDD}$ = 3.3 V, $nSLEEP$ = 1, All High-Side FETs = 'ON', $SPI$ = 'ON' (5 MHz), $T_A$ = 125 °C           |         |      | 5        | mA   |

| t <sub>WAKE</sub>  | Wake-up time                   | nSLEEP high to SPI ready                                                                                                      |         |      | 200      | μs   |

| t <sub>SLEEP</sub> | Turnoff time                   | nSLEEP low to device sleep                                                                                                    |         |      | 20       | μs   |

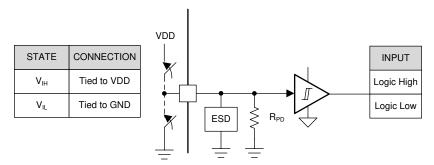

| LOGIC-LE           | VEL INPUTS (nSLEEP, SCLK, SDI) |                                                                                                                               |         |      |          |      |

| $V_{IL}$           | Input logic low voltage        |                                                                                                                               | 0       |      | 0.3*VDD  | V    |

| $V_{IH}$           | Input logic high voltage       |                                                                                                                               | 0.7*VDD |      | VDD      | V    |

| $V_{HYS}$          | Input logic hysteresis         |                                                                                                                               | 200     |      |          | mV   |

| I <sub>IL</sub>    | Input logic low current        | V <sub>IN</sub> = 0 V                                                                                                         | -1      |      | 1        | μΑ   |

| I <sub>IH</sub>    | Input logic high current       | $V_{IN} = V_{VDD}$                                                                                                            |         | 34   | 75       | μΑ   |

| $C_{ID}$           | Input capacitance              |                                                                                                                               |         |      | 15       | pF   |

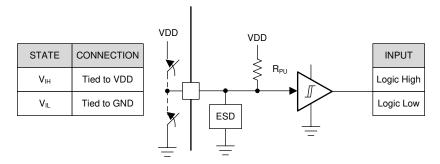

| LOGIC-LE           | VEL INPUTS (nSCS)              |                                                                                                                               |         |      |          |      |

| $V_{IL}$           | Input logic low voltage        |                                                                                                                               | 0       |      | 0.3*VDD  | V    |

| V <sub>IH</sub>    | Input logic high voltage       |                                                                                                                               | 0.7*VDD |      | VDD      | V    |

| V <sub>HYS</sub>   | Input logic hysteresis         |                                                                                                                               | 200     |      |          | mV   |

| I <sub>IL</sub>    | Input logic low current        | $V_{IN} = 0 V$                                                                                                                |         | 34   | 75       | μΑ   |

## **Electrical Characteristics (continued)**

at  $T_J = -40^{\circ}\text{C}$  to +150°C,  $V_{VM} = 4.5$  to 32 V (Main Supply),  $V_{VDD} = 3$  to 5.5 V (Logic Supply) (unless otherwise noted). Typical limits apply for  $T_A = 25^{\circ}\text{C}$ ,  $V_{VM} = 13.5$  V,  $V_{VDD} = 3.3$  V

|                       | PARAMETER                                    | TEST CONDITIONS                                                                                      | MIN     | TYP  | MAX                                                                                                                     | UNIT |

|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------|------|

| I <sub>IH</sub>       | Input logic high current                     | $V_{IN} = V_{VDD}$                                                                                   | -1      |      | 1                                                                                                                       | μΑ   |

| $C_{ID}$              | Input capacitance                            |                                                                                                      |         |      | 15                                                                                                                      | pF   |

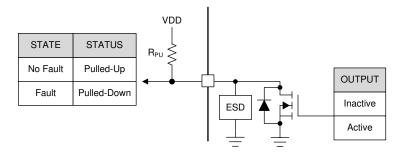

| OPEN-DRAI             | N OUTPUTS (nFAULT)                           |                                                                                                      |         |      |                                                                                                                         |      |

| $V_{OL}$              | Output logic low voltage                     | $I_{OD} = 5 \text{ mA}$                                                                              | 0       |      | 0.4                                                                                                                     | V    |

| I <sub>OH</sub>       | Output logic high current                    | V <sub>OD</sub> = 5 V                                                                                | -1      |      | 1                                                                                                                       | μΑ   |

| $C_{OD}$              | Output capacitance                           |                                                                                                      |         |      | 15                                                                                                                      | pF   |

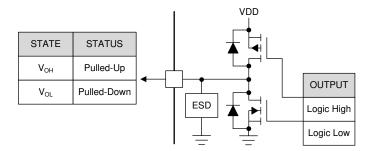

| PUSH-PULL             | OUTPUTS (SDO)                                |                                                                                                      |         |      | ·                                                                                                                       |      |

| V <sub>OL</sub>       | Output logic low voltage                     | $I_{OP} = 5 \text{ mA}$                                                                              | 0       |      | 0.4                                                                                                                     | V    |

| $V_{OH}$              | Output logic high voltage                    | $I_{OP} = 5 \text{ mA}$                                                                              | VDD-0.6 |      | VDD                                                                                                                     | V    |

| I <sub>OL</sub>       | Output logic low current                     | $V_{OP} = 0 V$                                                                                       | -1      |      | 1                                                                                                                       | μΑ   |

| I <sub>OH</sub>       | Output logic high current                    | $V_{OP} = V_{VDD}$                                                                                   | -1      |      | 1                                                                                                                       | μΑ   |

| C <sub>OD</sub>       | Output capacitance                           |                                                                                                      |         |      | 30                                                                                                                      | pF   |

| DRIVER OU             | TPUTS (OUTx)                                 |                                                                                                      |         |      |                                                                                                                         |      |

|                       | High side MOCEET on resistance               | V <sub>VM</sub> = 13.5 V, I <sub>OUT</sub> = 0.5 A, T <sub>A</sub> = 25°C                            |         | 0.75 | 1.1                                                                                                                     | Ω    |

| D                     | High-side MOSFET on resistance               | V <sub>VM</sub> = 13.5 V, I <sub>OUT</sub> = 0.5 A, T <sub>A</sub> = 125°C                           |         |      | 1.5                                                                                                                     | Ω    |

| R <sub>DS(ON)</sub>   | Low side MOSEET on registance                | V <sub>VM</sub> = 13.5 V, I <sub>OUT</sub> = 0.5 A, T <sub>A</sub> = 25°C                            |         | 0.75 | 1.1                                                                                                                     | Ω    |

|                       | Low-side MOSFET on resistance                | V <sub>VM</sub> = 13.5 V, I <sub>OUT</sub> = 0.5 A, T <sub>A</sub> = 125°C                           |         |      | 1.5                                                                                                                     | Ω    |

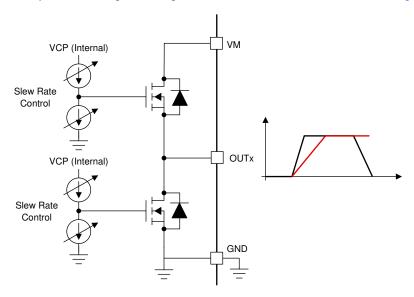

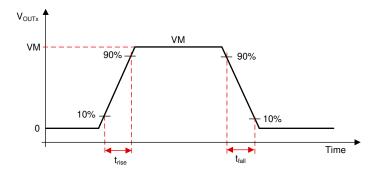

| OD                    | Output rise and fall time (high-side         | $V_{VM}$ = 13.5 V, 10-90%, $R_{LOAD}$ = 27 $\Omega$ , HBx_SR = 0b                                    |         | 0.6  |                                                                                                                         | V/µs |

| SR                    | and low-side)                                | $V_{VM}$ = 13.5 V, 10-90%, $R_{LOAD}$ = 27 $\Omega$ , HBx_SR = 1b                                    |         | 2.5  |                                                                                                                         | V/µs |

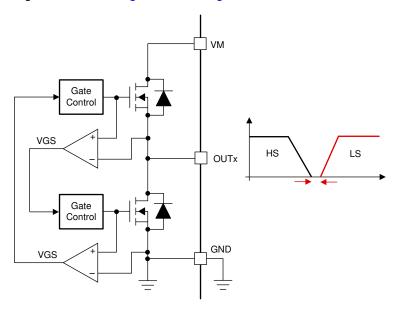

|                       | Output dead time (high to low / low to high) | V <sub>VM</sub> = 13.5 V, SR = 0, HS/LS driver<br>OFF to LS/HS driver ON                             | 8       | 20   | 32                                                                                                                      | μs   |

| <sup>t</sup> DEAD     |                                              | V <sub>VM</sub> = 13.5 V, SR = 1, HS/LS driver<br>OFF to LS/HS driver ON                             | 2       | 5    | 15                                                                                                                      | μs   |

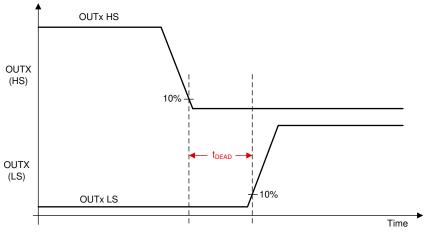

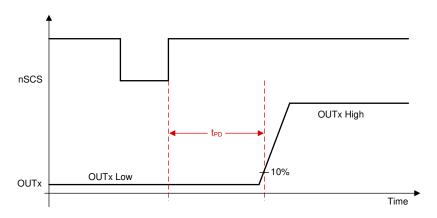

|                       | Propagation delay (high-side /               | High-side ON or low-side ON command (SPI last transition) to OUTx transition from Hi-Z state, SR = 0 | 5       | 12   | 25                                                                                                                      | μs   |

| t <sub>PD</sub>       | low-side ON/OFF)                             | High-side ON or low-side ON command (SPI last transition) to OUTx transition from Hi-Z state, SR = 1 | 3       | 5    | 10                                                                                                                      | μs   |

|                       |                                              | V <sub>OUTx</sub> = 13.5 V, nSLEEP = 1, SR = 0b                                                      |         | 6    | VDD  1 1 30 0.75 1.1 1.5 0.75 1.1 1.5 0.6 2.5 20 32 5 15 12 25 5 10 6 10 20 35 4 15 2 2 80 104 100 130 200 260 000 2600 | μA   |

|                       | Leakage current low-side                     | V <sub>OUTx</sub> = 13.5 V, nSLEEP = 1, SR = 1b                                                      |         | 20   | 35                                                                                                                      | μA   |

| I <sub>LEAK</sub>     |                                              | V <sub>OUTx</sub> = 13.5 V, nSLEEP = 0                                                               |         | 4    | 15                                                                                                                      | μA   |

|                       |                                              | V <sub>OUTx</sub> = 0 V, nSLEEP = 1                                                                  |         |      | 2                                                                                                                       | μA   |

|                       | Leakage current high-side                    | V <sub>OUTx</sub> = 0 V, nSLEEP = 0                                                                  |         |      | 2                                                                                                                       | μΑ   |

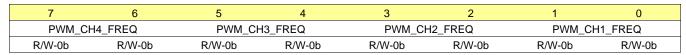

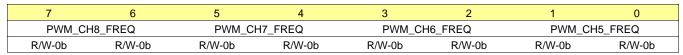

| PWM MODE              |                                              |                                                                                                      |         |      | •                                                                                                                       |      |

|                       |                                              | PWM_CHx_FREQ = 00b                                                                                   | 56      | 80   | 104                                                                                                                     | Hz   |

| ,                     | DIAMA control in a f                         | PWM_CHx_FREQ = 01b                                                                                   | 70      | 100  | 130                                                                                                                     | Hz   |

| f <sub>PWM</sub>      | PWM switching frequency                      | PWM_CHx_FREQ = 10b                                                                                   | 140     | 200  | 260                                                                                                                     | Hz   |

|                       |                                              | PWM_CHx_FREQ = 11b                                                                                   | 1400    | 2000 | 2600                                                                                                                    | Hz   |

| PROTECTIO             | ON CIRCUITS                                  |                                                                                                      |         |      | <u>'</u>                                                                                                                |      |

| \ /                   | Supply undervoltage lockout                  | Supply rising                                                                                        | 4.0     |      | 4.5                                                                                                                     | V    |

| $V_{UVLO}$            | (UVLO)                                       | Supply falling                                                                                       | 3.8     |      | 4.3                                                                                                                     | V    |

| V <sub>UVLO_HYS</sub> | Supply undervoltage lockout hysteresis       | Rising to falling theshold                                                                           |         | 200  |                                                                                                                         | mV   |

| t <sub>UVLO</sub>     | Supply undervoltage deglitch time            |                                                                                                      |         | 10   |                                                                                                                         | μs   |

## **Electrical Characteristics (continued)**

at  $T_J = -40^{\circ}\text{C}$  to +150°C,  $V_{VM} = 4.5$  to 32 V (Main Supply),  $V_{VDD} = 3$  to 5.5 V (Logic Supply) (unless otherwise noted). Typical limits apply for  $T_A = 25^{\circ}\text{C}$ ,  $V_{VM} = 13.5$  V,  $V_{VDD} = 3.3$  V

|                      | PARAMETER                                           | TEST CONDITIONS                                                                                                | MIN  | TYP | MAX  | UNIT |

|----------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-----|------|------|

|                      |                                                     | Supply rising, EXT_OVP = 0b                                                                                    | 21   |     | 25   | V    |

| $V_{OVP}$            | Supply overvoltage protection                       | Supply falling, EXT_OVP = 0b                                                                                   | 20   |     | 24   | V    |

|                      | (OVP)                                               | Supply rising, EXT_OVP = 1b                                                                                    | 32.7 |     | 35   | V    |

|                      |                                                     | Supply falling, EXT_OVP = 1b                                                                                   | 32   |     | 34.3 | V    |

| ,                    | Supply overvoltage protection hysteresis            | Rising to falling theshold, EXT_OVP = 0b                                                                       |      | 1   |      | V    |

| OVP_HYS              |                                                     | Rising to falling the shold, EXT_OVP = 1b                                                                      |      | 0.7 |      | V    |

| OVP                  | Supply overvoltage deglitch time                    |                                                                                                                |      | 10  |      | μs   |

| ,                    | La sia sandamaka sa (DOD)                           | Supply rising                                                                                                  | 2.45 |     | 3    | V    |

| POR                  | Logic undervoltage (POR)                            | Supply falling                                                                                                 | 2.4  |     | 2.95 | V    |

| / <sub>POR_HYS</sub> | Logic undervoltage hysteresis                       | Rising to falling theshold                                                                                     |      | 75  |      | mV   |

| OCP                  | Overcurrent protection trip point <sup>(1)(2)</sup> |                                                                                                                | 1.3  | 1.8 | 2.3  | Α    |

|                      |                                                     | OCP_DEG = 000b                                                                                                 | 6    | 10  | 14   | μs   |

|                      |                                                     | OCP_DEG = 001b                                                                                                 | 2.6  | 5   | 7.9  | μs   |

|                      |                                                     | OCP_DEG = 010b                                                                                                 | 0.4  | 2.5 | 5.9  | μs   |

|                      | Overcurrent protection deglitch time                | OCP_DEG = 011b                                                                                                 | 0.1  | 1   | 3.4  | μs   |

| OCP                  |                                                     | OCP_DEG = 100b                                                                                                 | 38.2 | 60  | 76.6 | μs   |

|                      |                                                     | OCP_DEG = 101b                                                                                                 | 23.1 | 40  | 51.9 | μs   |

|                      |                                                     | OCP DEG = 110b                                                                                                 | 18.5 | 30  | 41.5 | μs   |

|                      |                                                     | OCP DEG = 111b                                                                                                 | 8.4  | 20  | 31.6 | μs   |

| OLD                  | Open load detection current                         | Current flowing from VM to OUTx (High-<br>Side = ON) or OUTx to GND (Low-Side<br>= ON)                         | 2    | 9   | 18   | mA   |

| OLD_NEG              | Negative open load detection current                | Current flowing from OUTx to VM (High-<br>Side = ON) or GND to OUTx (Low-Side<br>= ON)                         | 2    | 15  | 30   | mA   |

| OLD_LOW              | Open load detection current in low current OLD mode | Current flowing from VM to OUTx (High-<br>Side = ON) or OUTx to GND (Low-Side<br>= ON)                         | 0.2  | 0.8 | 2    | mA   |

| OL_GND               | Passive OLD current                                 | DRV8908/6/4, FETs in Hi-Z state, current from OUTx to GND during OLD trip                                      |      | 113 |      | μΑ   |

| OL_GND               | Passive OLD voltage threshold                       | DRV8908/6/4, FETs in Hi-Z state,<br>voltage at OUTx during OLD trip for<br>GND-connected load                  |      | 3.3 |      | V    |

| OL_VM                | Passive OLD current                                 | DRV8908/6/4, FETs in Hi-Z state,<br>current from VM to OUTx for OLD trip,<br>HBX_VM_POLD = 0b                  |      | 118 |      | μA   |

| / <sub>OL_VM</sub>   | Passive OLD voltage threshold                       | DRV8908/6/4, FETs in Hi-Z state, voltage at OUTx during OLD trip for VM-connected load, HBX_VM_POLD = 0b       |      | 1.2 |      | V    |

| OL_VM                | Passive OLD current                                 | DRV8908/6/4, FETs in Hi-Z state,<br>current from VM to OUTx for OLD trip,<br>HBX_VM_POLD = 1b                  |      | 547 |      | μΑ   |

| √ <sub>OL_VM</sub>   | Passive OLD voltage threshold                       | DRV8908/6/4, FETs in Hi-Z state,<br>voltage at OUTx during OLD trip for VM<br>connceted load, HBX_VM_POLD = 1b |      | 1.8 |      | V    |

<sup>(1)</sup> For  $20\text{-V} < V_{VM} < 28\text{-V}$ , the OCP deglicth time must be limited to  $10\text{-}\mu\text{s}$  (Default Deglitch Value, OCP\_DEG = 000b). (2) For  $V_{VM} > 28$  V, the OCP deglitch time must be limited to  $1\text{-}\mu\text{s}$  (Lowest Deglitch Value, OCP\_DEG = 011b).

## **Electrical Characteristics (continued)**

at  $T_J = -40$ °C to +150°C,  $V_{VM} = 4.5$  to 32 V (Main Supply),  $V_{VDD} = 3$  to 5.5 V (Logic Supply) (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{VM} = 13.5$  V,  $V_{VDD} = 3.3$  V

|                       | PARAMETER                               | TEST CONDITIONS                                                         | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>OL</sub>       | Passive OLD detect resistance threshold | DRV8908/6/4, FETs in Hi-Z state, Full bridge connection                 | 5   |     | 100 | kΩ   |

| R <sub>OL</sub>       | Passive OLD detect resistance threshold | DRV8908/6/4, FETs in Hi-Z State, Load connected to GND                  | 5   |     | 100 | kΩ   |

| R <sub>OL</sub>       | Passive OLD detect resistance threshold | DRV8908/6/4, FETs in Hi-Z State, Load connected to VM, HBX_VM_POLD = 0b | 5   |     | 400 | kΩ   |

| R <sub>OL</sub>       | Passive OLD detect resistance threshold | DRV8908/6/4, FETs in Hi-Z State, Load connected to VM, HBX_VM_POLD = 1b | 5   |     | 100 | kΩ   |

| t <sub>OLD</sub>      | Open load deglitch time                 | Active OLD (Continuous Mode)                                            | 2   | 3   | 4   | ms   |

| t <sub>OLD</sub>      | Open load deglitch time                 | Active OLD (PWM Mode)                                                   | 150 | 200 | 300 | μs   |

| T <sub>OTW</sub>      | Thermal warning temperature             | Die temperature (T <sub>j</sub> )                                       | 120 | 140 | 170 | °C   |

| T <sub>OTW_HYS</sub>  | Thermal warning hysteresis              | Die temperature (T <sub>j</sub> )                                       |     | 20  |     | °C   |

| T <sub>OTSD</sub>     | Thermal shutdown temperature            | Die temperature (T <sub>j</sub> )                                       | 150 | 175 | 200 | °C   |

| T <sub>OTSD_HYS</sub> | Thermal shutdown hysteresis             | Die temperature (T <sub>j</sub> )                                       |     | 20  |     | °C   |

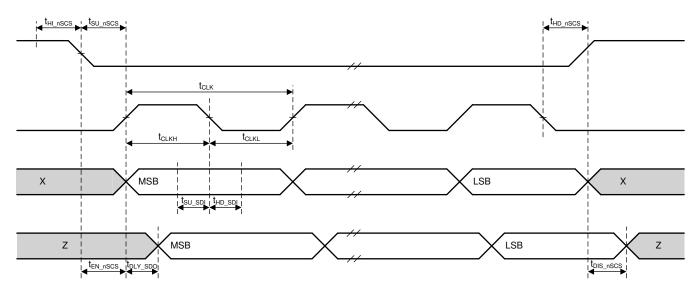

## 7.6 Timing Requirements

|                       | ning requirements                        | TEST COMPLETIONS                |     | NOM MAN |      |

|-----------------------|------------------------------------------|---------------------------------|-----|---------|------|

|                       | PARAMETER                                | TEST CONDITIONS                 | MIN | NOM MAX | UNIT |

| SPI (nSCS             | , SCLK, SDI, SDO)                        |                                 |     |         |      |

| t <sub>READY</sub>    | SPI ready after after enable             | VM > UVLO, ENABLE = 3.3 V       |     | 1       | ms   |

| t <sub>CLK</sub>      | SCLK minimum period                      |                                 | 200 |         | ns   |

| t <sub>CLKH</sub>     | SCLK minimum high time                   |                                 | 100 |         | ns   |

| t <sub>CLKL</sub>     | SCLK minimum low time                    |                                 | 100 |         | ns   |

| t <sub>SU_SDI</sub>   | SDI input data setup time                |                                 | 40  |         | ns   |

| t <sub>HD_SDI</sub>   | SDI input data hold time                 |                                 | 60  |         | ns   |

| t <sub>DLY_SDO</sub>  | SDO output data delay time               | SCLK high to SDO valid          |     | 60      | ns   |

| t <sub>SU_nSCS</sub>  | nSCS input setup time                    |                                 | 100 |         | ns   |

| t <sub>HD_nSCS</sub>  | nSCS input hold time                     |                                 | 100 |         | ns   |

| t <sub>HI_nSCS</sub>  | nSCS minimum high time before active low |                                 | 600 |         | ns   |

| t <sub>DIS_nSCS</sub> | nSCS disable delay time                  | nSCS high to SDO high impedance |     | 30      | ns   |

| t <sub>SC_SPI</sub>   | Successive SPI write gaps                |                                 |     | 2.5     | μs   |

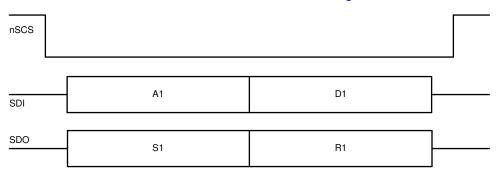

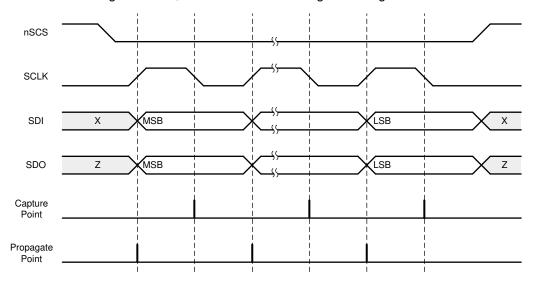

Figure 1. SPI Timing

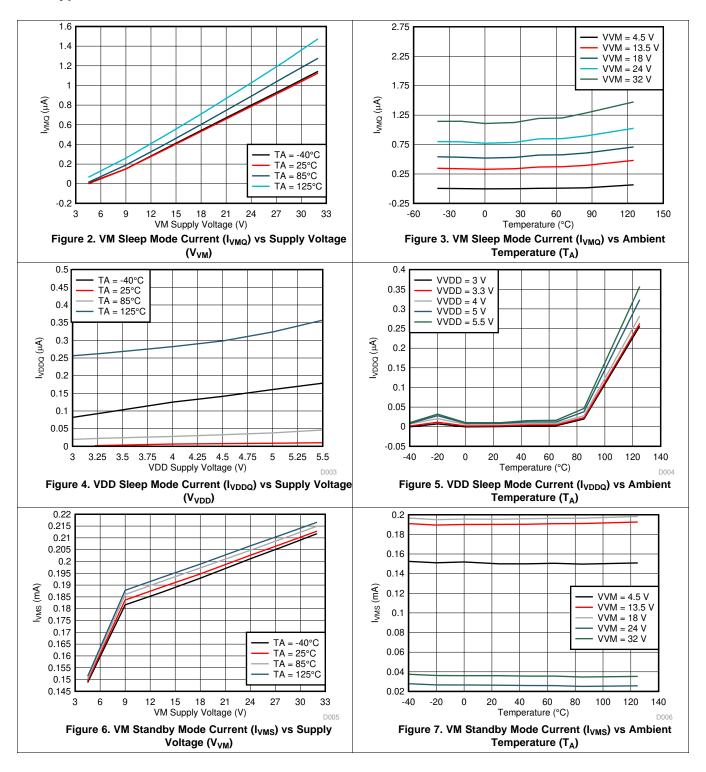

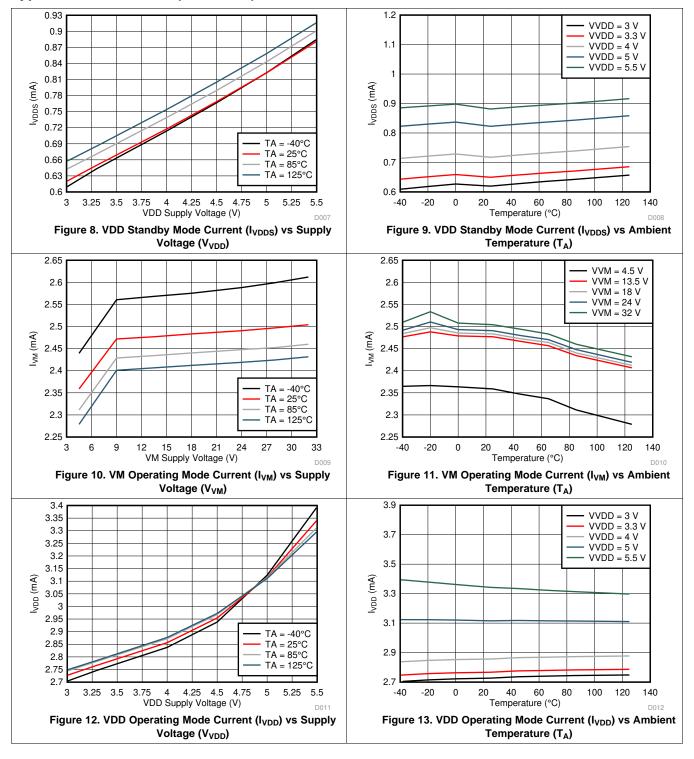

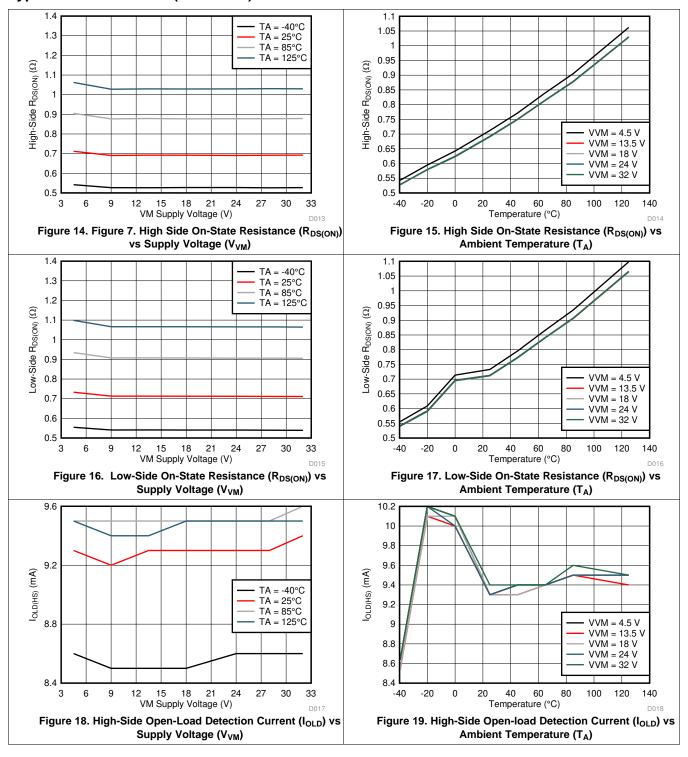

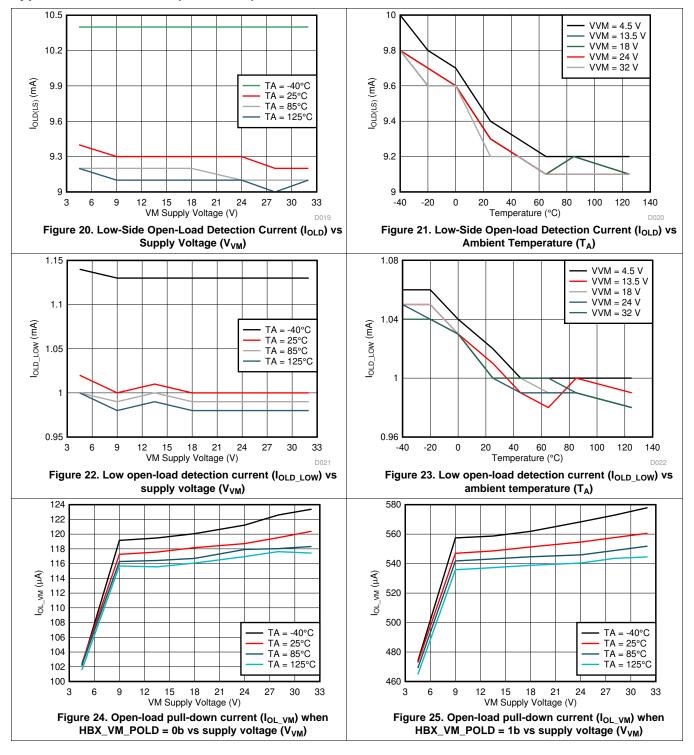

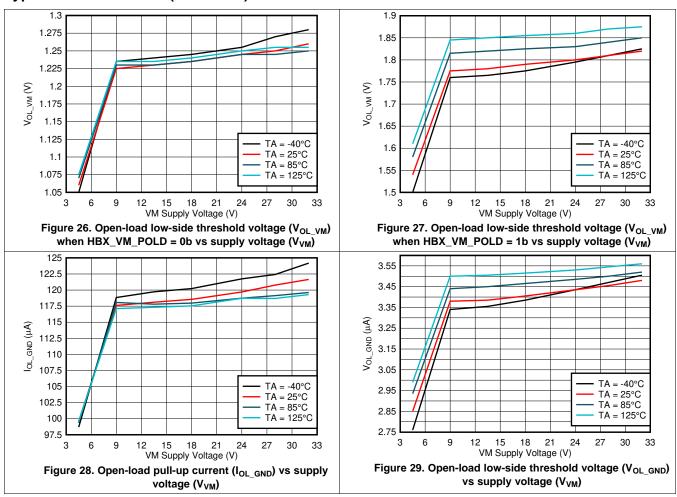

### 7.7 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

The DRV89xx-Q1 family are 4.5-V to 32-V integrated multi half-bridge drivers which supports a maximum voltage of 40-V for load-dump scenario. The half-bridges are designed to support 1-A per half-bridge and 6-A from the VM/GND pins. The DRV89xx family offers drivers from 4 to 12 half-bridge outputs.

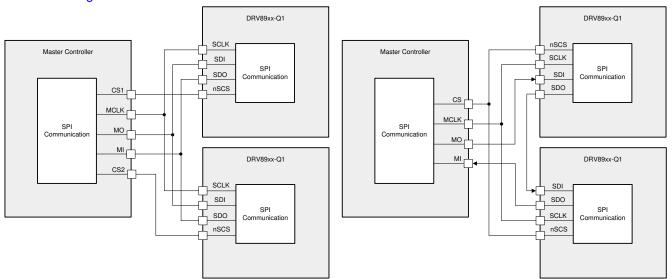

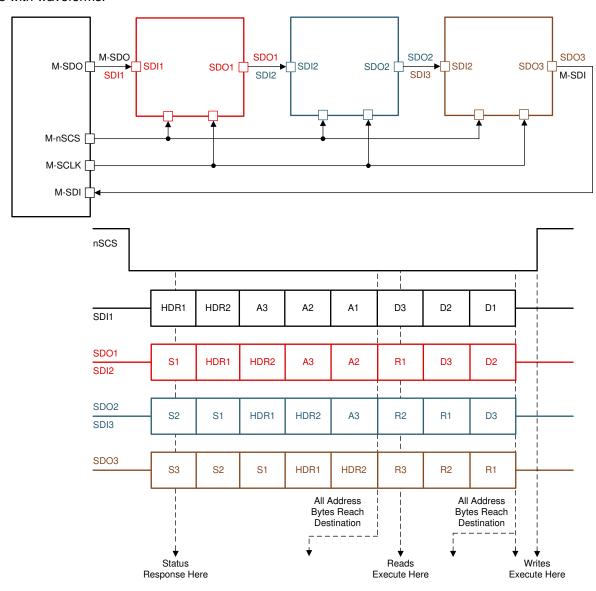

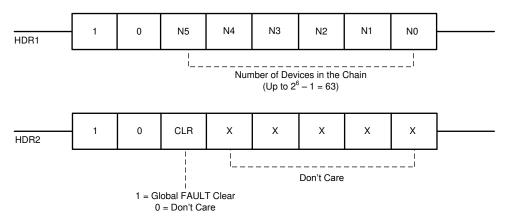

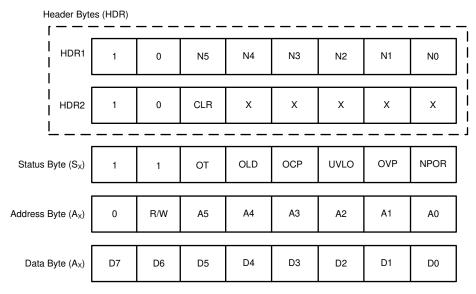

A standard 16-bit, 5-MHz serial peripheral interface (SPI) provides a simple method for configuring the various device settings and reading fault diagnostic information through an external controller. The device is also equipped with a daisy-chain functionality which allows connecting multiple devices using a single nSCS line and saving on multiple resources.

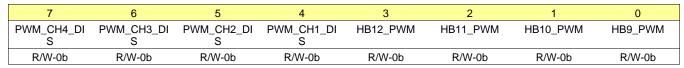

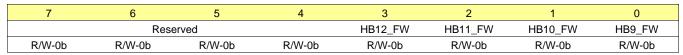

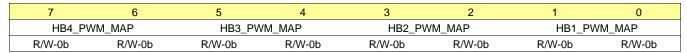

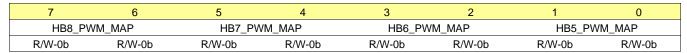

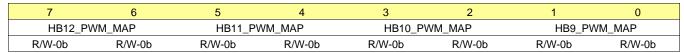

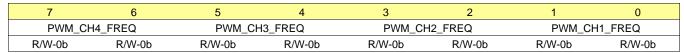

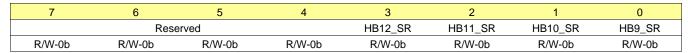

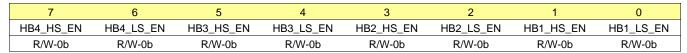

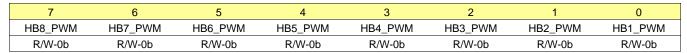

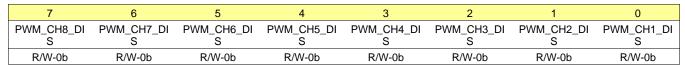

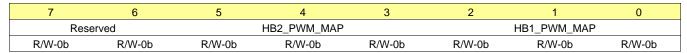

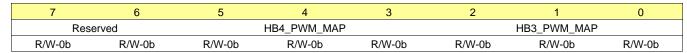

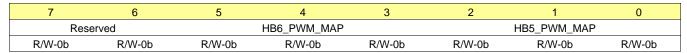

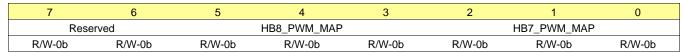

This device has 4 internal PWM generators (DRV8912-Q1 and DRV8910-Q1) or 8 internal PWM generators (DRV8908-Q1, DRV8906-Q1 and DRV8904-Q1) which can be mapped to any of the half-bridge through SPI registers. The PWM frequency (4 options) and duty (8-bit resolution) for each channel can be selected using the SPI registers. This PWM mode is useful for implementing the current control of motor or dimming control of LEDs.

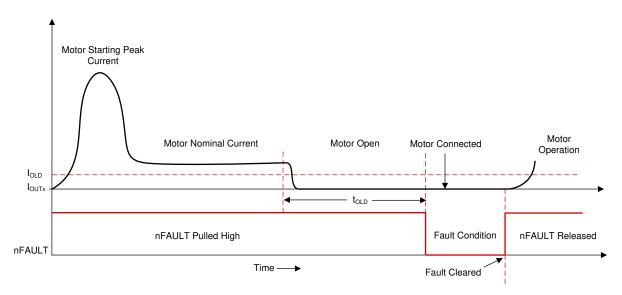

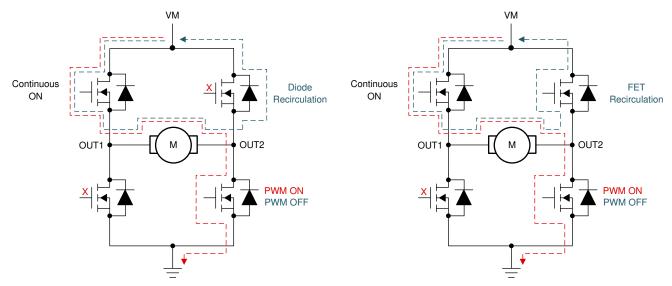

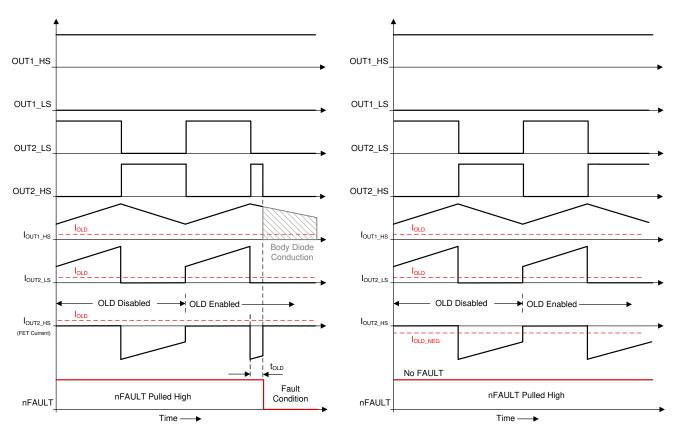

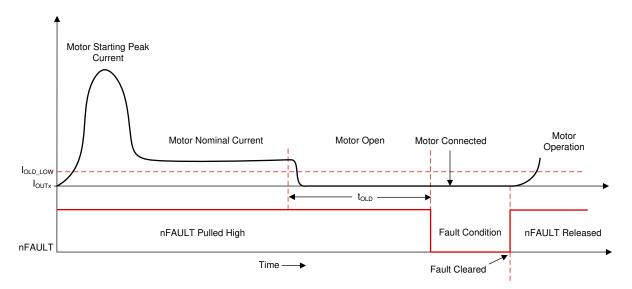

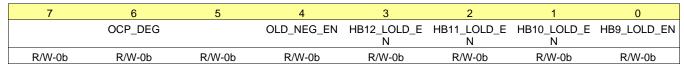

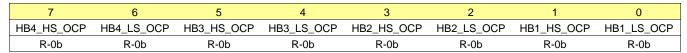

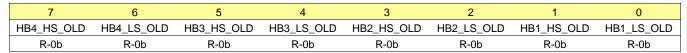

The device also has numerous integrated protection features which protects the device in case of any abnormal scenario. The over-current protection (OCP) ensures the device protection in any short scenarios like the phase short, phase to ground short and phase to supply short conditions. Undervoltage lockout (UVLO) and overvoltage protection (OVP) ensures the driver operation in fluctuating voltages to support the crank-start and load-dump scenario in automotive applications. In addition to this, the open-load detection (OLD) feature ensure the proper load connection. All devices support active OLD, low-current OLD, and negative-current OLD. Passive OLD is only supported on DRV8908-Q1, DRV8906-Q1 and DRV8904-Q1 devices. Device faults are indicated on the nFAULT pin, and detailed information is available in the device SPI registers.

The device integrates a spread spectrum clocking feature for both the internal digital oscillator and internal charge pump. This feature combined with programmable output slew-rate control minimizes the radiated emissions from the device.

The device is available in a 24-pin HTSSOP package with a thermal pad.

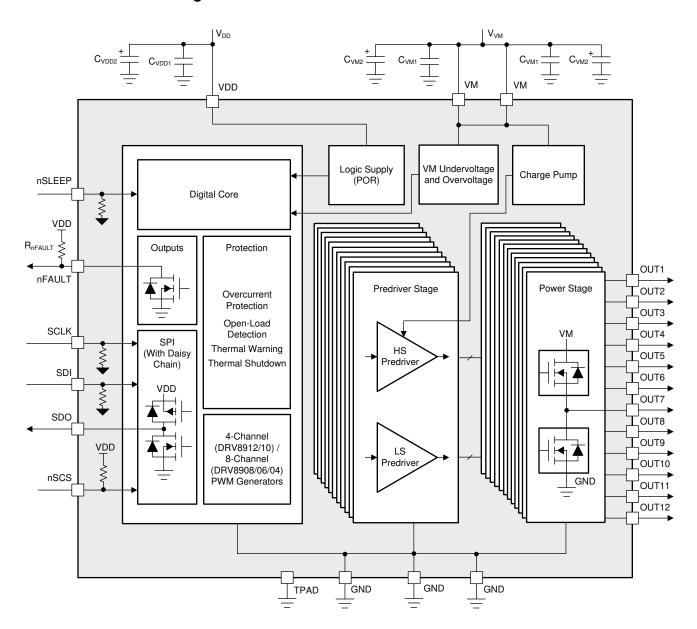

## 8.2 Functional Block Diagram

## 8.3 Feature Description

Table 1 lists the recommended values of the external components for the driver.

Table 1. DRV89xx-Q1 Driver External Components

| COMPONENTS          | PIN 1 | PIN 2  | RECOMMENDED                            |  |  |

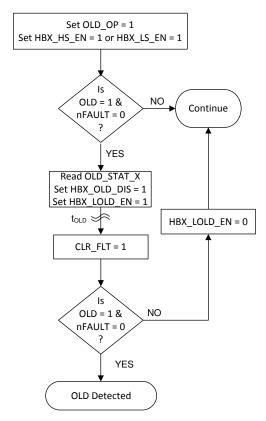

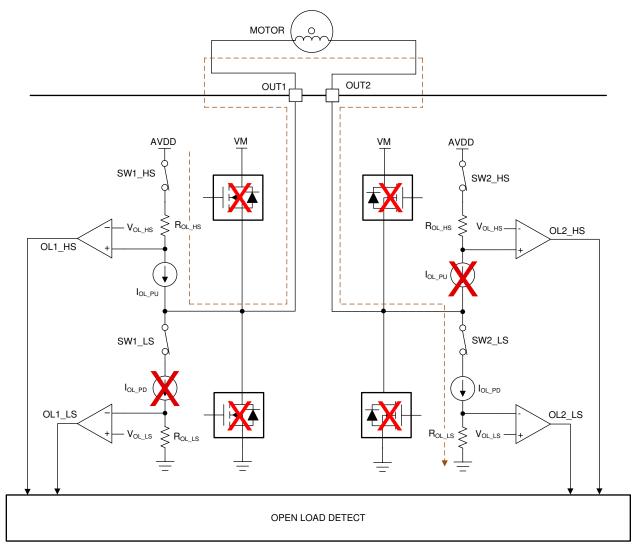

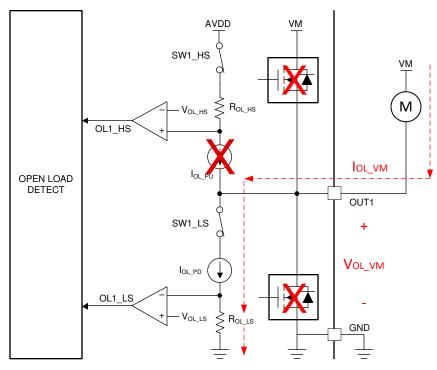

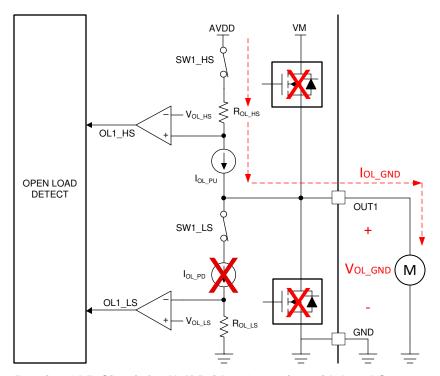

|---------------------|-------|--------|----------------------------------------|--|--|