## 4.1-40V 160-mΩ Quad-Channel Smart High-Side Switch

#### **FEATURES**

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 1: -40°C to 125°C **Ambient Operating Temperature Range**

- Quad-Channel 160-mΩ Smart High-Side Switch With Full Diagnostics

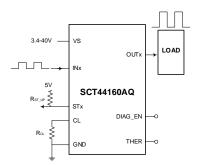

- A Version: Open-Drain Digital Output

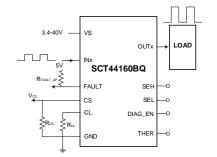

- B Version: Current Sense Analog Output

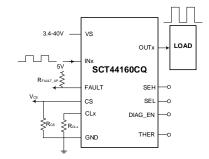

- C Version: Current Sense Analog Output +4 CL pin for each channel

- Wide Operating Voltage: 4.1 V to 40 V

- High accurate current sense: ±15% @ 500mA, ±30% @ 50mA with B Version and C Version

- Adjustable current limit: ±30% when > 250mA, ±15% when > 500mA

- Protection:

- Short-to-GND Protection by Current Limit (Internal or External)

- Thermal Shutdown With Latch-Off Option and Thermal Swing

- Inductive Load Negative Voltage Clamp with Optimized Slew Rate

- Loss-of-GND and Loss-of-Battery Protection

- Diagnostic:

- Overcurrent and Short-to-Ground Detection

- Open Load / Short to Battery Detection During On and Off State

- Global Fault Report for Fast Hardware Interrupt

- Available in an ETSSOP-28 Package

#### APPLICATIONS

- High-Side Relay Drivers

- Power Switch for Sub-Module Power Supply

- Low Wattage Lamp Power Switch

- General Resistive, Inductive, and Capacitive Loads

#### DESCRIPTION

The SCT44160Q device is fully protected quadchannel smart high-side switch with four integrated 160-m $\Omega$  NMOS power FETs.

For version A, the device implements the digital fault report with an open-drain structure, Quad channel synchronous setting of current limit value.

For version B, the device achieves high-precision current detection, making diagnosis more accurate, Quad channel synchronous setting of current limit value.

For version C, the device can achieve high-precision current detection while setting current limits for each channel separately.

The SCT44160Q provides current limit, thermal shutdown protection. Full diagnostics and highaccuracy current sense enable intelligent control of the load. The device is available in a 28-pin ETSSOP-28 package.

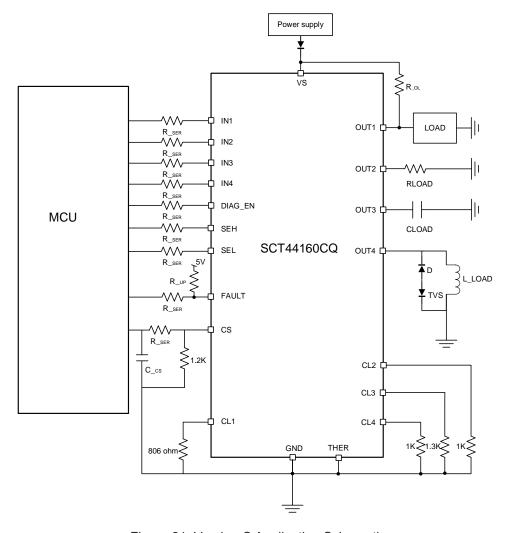

#### TYPICAL APPLICATION

Typical Application of Version A

Typical Application of Version B

Typical Application of Version C

# SCT44160Q

## **REVISION HISTORY**

Revision 0.8: Customer Sample Revision 0.81: Update EC table Revision 0.82: Update EC table

Revision 0.83: Update Package name

Revision 0.84: Update Device Order Information

#### **DEVICE ORDER INFORMATION**

| ORDERABLE<br>DEVICE | PACKAGING<br>TYPE | STANDARD<br>PACK QTY | PACKAGE<br>MARKING | PINS | PACKAGE<br>DESCRIPTION |

|---------------------|-------------------|----------------------|--------------------|------|------------------------|

| SCT44160AQMZER      | Tape & Reel       | 4000                 | 160AQ              | 28   | ETSSOP-28              |

| SCT44160BQMZER      | Tape & Reel       | 4000                 | 160BQ              | 28   | ETSSOP-28              |

| SCT44160CQMZER      | Tape & Reel       | 4000                 | 160CQ              | 28   | ETSSOP-28              |

## ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                                                | MIN  | MAX | UNIT |

|----------------------------------------------------------------------------|------|-----|------|

| VS (t < 400 mS)                                                            | -0.3 | 45  | V    |

| Reverse polarity voltage                                                   | -36  |     | V    |

| Current on GND (t < 2 minutes)                                             | -100 | 250 | mA   |

| Voltage on INx, DIAG_EN, SEL, SEH, and THER                                | -0.3 | 7   | V    |

| Current on INx, DIAG_EN, SEL, SEH, and THER                                | -10  |     | mA   |

| Voltage on STx or FAULT                                                    | -0.3 | 7   | V    |

| Current on STx or FAULT                                                    | -30  | 10  | mA   |

| Voltage on CS                                                              | 2.7  | 7   | V    |

| Current on CS                                                              |      | 30  | mA   |

| Voltage on CL, CL1, CL2, CL3, CL4                                          | -0.3 | 7   | V    |

| Current on CL, CL1, CL2, CL3, CL4                                          |      | 6   | mA   |

| Inductive load switch-off energy dissipation, single pulse, single channel |      | 40  | mJ   |

| Junction temperature <sup>(2)</sup>                                        | -40  | 150 | °C   |

| Storage temperature T <sub>STG</sub>                                       | -65  | 150 | °C   |

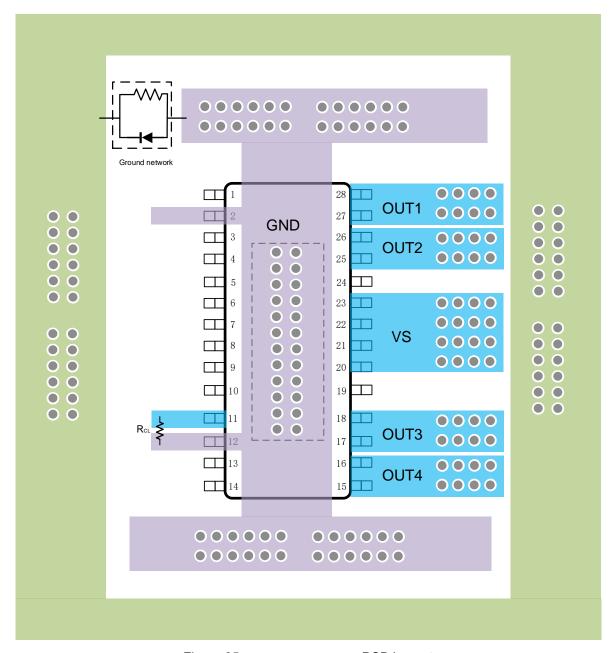

## PIN CONFIGURATION

Top View: Version A ETSSOP-28

Top View: Version B ETSSOP-28

Top View: Version B ETSSOP-28

The IC includes thermal shutdown protection to protect the device during overload conditions. Junction temperature will exceed 170°C when thermal shutdown protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

# **SCT44160Q**

# **PIN FUNCTIONS**

| NAME    |             | NO.         |             | I/O <sup>(1)</sup> | DIN FUNCTION                                                                                 |

|---------|-------------|-------------|-------------|--------------------|----------------------------------------------------------------------------------------------|

| NAME    | A Version   | B Version   | C Version   | 10(1)              | PIN FUNCTION                                                                                 |

| GND     | 1,12        | 1,12        | 1,12        | G                  | IC ground pin.                                                                               |

| NC      | 2,19,24     | 2,19,24     | -           | ı                  | Not Connection.                                                                              |

| CL1     | -           | -           | 2           | 0                  | Adjustable the current limit of channel 1.                                                   |

| IN1     | 3           | 3           | 3           | I                  | Channel 1 logic input, internal pulldown.                                                    |

| IN2     | 4           | 4           | 4           | I                  | Channel 2 logic input, internal pulldown.                                                    |

| IN3     | 5           | 5           | 5           | I                  | Channel 3 logic input, internal pulldown.                                                    |

| IN4     | 6           | 6           | 6           | - 1                | Channel 4 logic input, internal pulldown.                                                    |

| ST1     | 7           | -           | -           | 0                  | Open-drain diagnostic status output for channel 1, external pull-up voltage required.        |

| ST2     | 8           | -           | -           | 0                  | Open-drain diagnostic status output for channel 2, external pull-up voltage required.        |

| ST3     | 9           | -           | -           | 0                  | Open-drain diagnostic status output for channel 3, external pull-up voltage required.        |

| ST4     | 10          | -           | -           | 0                  | Open-drain diagnostic status output for channel 4, external pull-up voltage required.        |

| SEH     | -           | 7           | 7           | I                  | CS channel-selection high bit; internal pulldown.                                            |

| SEL     | -           | 8           | 8           | - 1                | CS channel-selection low bit; internal pulldown.                                             |

| FAULT   | -           | 9           | 9           | 0                  | Global fault report with open-drain structure, ORed logic for quad-channel fault conditions. |

| CS      | -           | 10          | 10          | 0                  | Current-sense output                                                                         |

| CL      | 11          | 11          | -           | 0                  | Adjustable current limits for quad channels                                                  |

| CL4     | -           | -           | 11          | 0                  | Adjustable the current limit of channel 4.                                                   |

| THER    | 13          | 13          | 13          | I                  | Thermal shutdown behavior control, latch off or auto-retry; internal pulldown.               |

| DIAG_EN | 14          | 14          | 14          | I                  | Enable-disable pin for diagnostics; internal pulldown.                                       |

| OUT4    | 15,16       | 15,16       | 15,16       | 0                  | Output of the channel 4 high side-switch, connected to the load.                             |

| OUT3    | 17,18       | 17,18       | 17,18       | 0                  | Output of the channel 3 high side-switch, connected to the load.                             |

| CL3     | -           | -           | 19          | 0                  | Adjustable the current limit of channel 3.                                                   |

| VS      | 20,21,22,23 | 20,21,22,23 | 20,21,22,23 | ı                  | Power supply; battery voltage.                                                               |

| CL2     |             |             |             | 0                  | Adjustable the current limit of channel 2.                                                   |

| OUT2    | 25,26       | 25,26       | 25,26       | 0                  | Output of the channel 2 high side-switch, connected to the load.                             |

| OUT1    | 27,28       | 27,28       | 27,28       | 0                  | Output of the channel 1 high side-switch, connected to the load.                             |

(1) G=Ground, I=Input, O=Output

## RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER                    | DEFINITION                     | MIN | MAX | UNIT |

|------------------------------|--------------------------------|-----|-----|------|

| V <sub>VS</sub>              | Input voltage range            | 4.1 | 40  | V    |

| INx, DIAG_EN, SEL, SHE, THER | External pull-up voltage range | 0   | 5   | V    |

| STx, FAULT                   | External pull-up voltage range | 0   | 5   | V    |

| Nominal dc load current      |                                | 0   | 1.5 | Α    |

| TJ                           | Operating junction temperature | -40 | 150 | °C   |

## **ESD RATINGS**

| PARAMETER        | DEFINITION                                                                                   | MIN | MAX | UNIT |

|------------------|----------------------------------------------------------------------------------------------|-----|-----|------|

| V <sub>ESD</sub> | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>     | -3  | +3  | kV   |

|                  | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -2  | +2  | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved 5

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## THERMAL INFORMATION

| PARAMETER               | THERMAL METRIC                                              | ETSSOP-28 | UNIT |

|-------------------------|-------------------------------------------------------------|-----------|------|

| Reja                    | Junction to ambient thermal resistance <sup>(1)</sup>       | 24.27     |      |

| ReJC (top)              | Junction to case (top) thermal resistance <sup>(1)</sup>    | 32.11     |      |

| R <sub>θ</sub> JC (bot) | Junction to case (bottom) thermal resistance <sup>(1)</sup> | 2.49      | °C/W |

| R <sub>θ</sub> ЈВ       | Junction to board thermal resistance <sup>(1)</sup>         | 9.17      |      |

| R <sub>ψJT</sub>        | Junction-to-top characterization parameter                  | 2.96      |      |

<sup>(1)</sup> SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT44160Q is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT44160Q. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JA}$  and  $R_{\theta JC}$ .

## **ELECTRICAL CHARACTERISTICS**

Typical values correspond to  $T_J = 25^{\circ}C$ . Minimum and maximum limits apply over the  $-40^{\circ}C$  to  $150^{\circ}C$  junction temperature range unless otherwise stated. VS = 13.5 V, INx = 5 V unless otherwise stated.

| SYMBOL                           | PARAMETER                               | TEST CONDITION MIN                                                                                              |     | TYP | MAX  | UNIT |

|----------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Power Sup                        | ply                                     |                                                                                                                 |     |     |      |      |

| Vvs                              | Operating input                         |                                                                                                                 | 4.1 |     | 40   | V    |

|                                  | Input UVLO Threshold                    | V <sub>VS</sub> rising                                                                                          |     | 3.8 | 4.05 | V    |

| Vvs_uvlo                         | Hysteresis                              |                                                                                                                 |     | 500 |      | mV   |

| I <sub>Q_OP</sub>                | Operating input                         | DIAG_EN=5V,I <sub>OUTx</sub> =0.5A, Current limit=2A,All channels on A version and B version                    |     | 7.5 |      | - mA |

| TQ_OP                            | current                                 | DIAG_EN=5V,I <sub>OUTx</sub> =0.5A, Current limit=2A,All channels on C version                                  |     | 9.5 |      | IIIA |

|                                  |                                         | INx=DIAG_EN=THER=0V, CL=CS=Floating                                                                             |     |     | 0.3  | uA   |

| I <sub>OFF</sub> Standby current |                                         | INx=DIAG_EN=THER=0V, CL=CS=Floating,TJ=125°C                                                                    |     |     | 3    | uA   |

| I <sub>OFF(DIAG)</sub>           | Standby current with diagnostic enabled | INx=THER=0V,DIAG_EN=5V, VS-<br>OUTx>V <sub>OL_OFF</sub>                                                         |     | 1   | 5    | mA   |

| toff(DIAG)                       | Standby mode deglitch time              | IN from high to low, if deglitch time >T <sub>OFF(DIAG)</sub> , the device enters into standby mode.            |     | 8   |      | mS   |

| I <sub>LKG_OUT</sub>             | Output leakage current in off-state     | INx=DIAG_EN=THER=OUTx=0V                                                                                        |     |     | 3    | uA   |

| Power Stag                       | je                                      |                                                                                                                 |     |     |      |      |

| RDSON                            | On-state resistance                     |                                                                                                                 |     | 160 |      | mΩ   |

| VF                               | Drain-source diode voltage              | INx=0V, IOUTx = -0.1 A                                                                                          |     | 0.7 |      |      |

| I <sub>CL(INT)</sub>             | Internal current limit                  | Internal current limit value, CL pin connected to GND                                                           | 7   |     | 14   | А    |

|                                  | Current limit during                    | Internal current limit value under thermal shutdown                                                             |     | 2   |      | Α    |

| I <sub>CL(TSD)</sub>             | thermal shutdown                        | External current limit value under thermal shutdown. The percentage of the external current limit setting value |     | 60% |      |      |

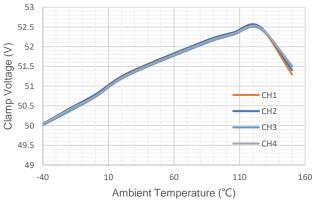

| V <sub>DS</sub> (clamp)          | Drain-to-source internal clamp voltage  |                                                                                                                 |     | 52  |      | V    |

For more information www.silicontent.com © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

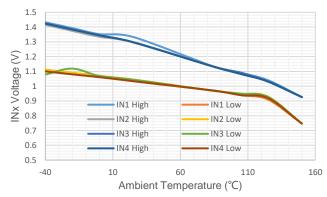

| Vih                  | Logic high-level voltage                                       |                                                                                                                         |      | 1.35 | 1.55                 | V  |

|----------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|----------------------|----|

| / <sub>IL</sub>      | Logic low-level voltage                                        |                                                                                                                         | 0.75 | 1.05 |                      | V  |

| RL PG IN             | INx-pin pulldown resistor                                      |                                                                                                                         |      | 180  |                      | kΩ |

| RL_PG_DIAG           | DIAG_EN-pin pulldown resistor                                  |                                                                                                                         |      | 240  |                      | kΩ |

| RL_PG_THER           | THER-pin pulldown resistor                                     |                                                                                                                         |      | 80   |                      | kΩ |

| Diagnostic           | s                                                              |                                                                                                                         |      |      |                      |    |

| I <sub>LKG _GL</sub> | Output leakage current under GND loss condition                |                                                                                                                         |      | 24   | 60                   | uA |

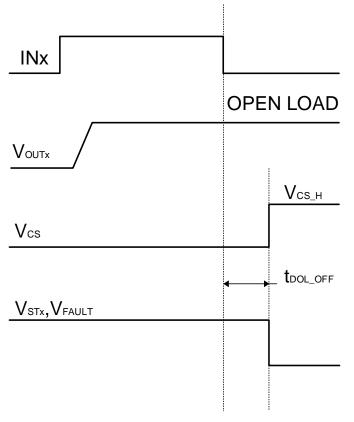

| Vol_off              | Open-load detection threshold                                  | IN = 0 V, when V <sub>VS</sub> – V <sub>OUTx</sub> < V <sub>OL_OFF</sub> ,<br>duration longer than t(ol,off), then open | 1.1  | 1.8  | 2.7                  | V  |

| t <sub>DOL_OFF</sub> | Open-load detection threshold deglitch time                    | load is detected, off state                                                                                             | 500  | 750  | 970                  | uS |

| I <sub>OL_OFF</sub>  | Off-state output sink current                                  | INx=0V,DIAG_EN=5V, V <sub>OUTx</sub> =V <sub>VS</sub>                                                                   |      | 43   | 55                   | uA |

| V <sub>OL_STx</sub>  | Status low-output voltage                                      | ISTx = 2 mA, version A only                                                                                             |      | 0.3  |                      | V  |

| Vol_fault            | Fault low-output voltage                                       | FAULT = 2 mA, version B, and version C                                                                                  |      | 0.3  |                      | ٧  |

| t <sub>CL_DEG</sub>  | Deglitch time when current limit occurs                        | INx = DIAG_EN = 5V, the deglitch time from current limit toggling to FAULT, STx, CS report.                             | 80   |      | 180                  | uS |

| T <sub>SD</sub>      | Thermal shutdown threshold                                     |                                                                                                                         |      | 175  |                      | °C |

| T <sub>SD_RST</sub>  | Thermal shutdown status reset threshold                        |                                                                                                                         |      | 155  |                      | °C |

| Tsw                  | Thermal swing shutdown threshold                               |                                                                                                                         |      | 40   |                      | °C |

| Тнүѕ                 | Hysteresis for resetting the thermal shutdown or thermal swing |                                                                                                                         |      | 10   |                      | °C |

| Current Lir          | nit                                                            |                                                                                                                         |      |      |                      |    |

| K <sub>CL</sub>      | Current-limit ratio                                            |                                                                                                                         |      | 2700 |                      |    |

| V <sub>CL</sub>      | Current limit internal threshold                               |                                                                                                                         |      | 0.8  |                      | ٧  |

| ∆Kcl/ Kcl            | External current limit                                         | I <sub>Limit</sub> ≥0.25A                                                                                               | 30   |      | 30                   | %  |

| ZINCL/ NCL           | accuracy                                                       | 0.5A ≤ I <sub>Limit</sub> ≤ 7A                                                                                          | 15   |      | 15                   | 70 |

| Current Se           | nse (Version B, C)                                             |                                                                                                                         |      |      |                      |    |

| Kcs                  | Current-sense ratio                                            |                                                                                                                         |      | 300  |                      |    |

|                      |                                                                | I <sub>OUTx</sub> ≥ 50mA                                                                                                | -30  |      | 30                   |    |

|                      |                                                                | I <sub>OUTx</sub> ≥ 100mA                                                                                               | -20  |      | 20                   |    |

|                      |                                                                | I <sub>OUTx</sub> ≥ 500mA                                                                                               | -15  |      | 15                   |    |

| \                    | Current-sense voltage                                          | V <sub>VS</sub> ≥ 6.5V                                                                                                  | 0    |      | 4                    | ., |

| Vcs_lin              | linear range                                                   | 5V ≤ V <sub>VS</sub> < 6.5V                                                                                             | 0    |      | V <sub>VS</sub> -2.5 | V  |

| lout_lin             | Output-current linear range                                    |                                                                                                                         | 0    |      | 2.5                  | Α  |

| Vcs_н                | Current sense pin output voltage                               | Fault mode                                                                                                              | 4.3  |      | 5.1                  | ٧  |

| I <sub>CS_H</sub>    | Current-sense pin output current                               | V <sub>CS</sub> =4.5V                                                                                                   | 10   | 22   |                      | m/ |

| lcs_Lkg              | Current-sense leakage current in disabled mode                 | DIAG_EN=0V,TJ=125°C                                                                                                     |      |      | 0.5                  | u/ |

# **SCT44160Q**

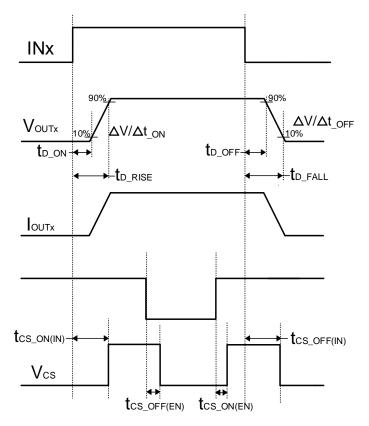

| Switching                 |                                                      |                                                                                                                  |        |      |

|---------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|------|

| t <sub>D_ON</sub>         | Input to output propagation delay, Rising            | DIAG_EN=5V, IOUTX =0.5A, INX rising edge to 10% of VOUTX                                                         | 30     | uS   |

| t <sub>D_OFF</sub>        | Input to output propagation delay, Falling           | DIAG_EN=5V, I <sub>OUTx</sub> =0.5A, INx falling edge to 90% of V <sub>OUTx</sub>                                | 5      | uS   |

| $\Delta$ V/ $\Delta$ t_on | Turnon slew rate                                     | DIAG_EN=5V, I <sub>OUTx</sub> =0.5A, V <sub>OUTx</sub> from 10% to 90%                                           | 0.3    | V/uS |

| ∆V/∆t_off                 | Turnoff slew rate                                    | DIAG_EN=5V, I <sub>OUTx</sub> =0.5A, V <sub>OUTx</sub> from 90% to 100%                                          | 0.4    | V/uS |

| t <sub>D_MATCH</sub>      | t <sub>D_RISE</sub> - t <sub>D_FALL</sub>            |                                                                                                                  | 20     | uS   |

| Current Se                | nse timing                                           |                                                                                                                  |        |      |

| tcs_on(en)                | CS settling time from DIAG_EN disabled               | I <sub>OUTx</sub> =0.5A, DIAG_EN rising edge to V <sub>CS</sub> rising                                           | 3 10   | ) uS |

| tcs_off(en)               | CS settling time from DIAG EN enabled                | I <sub>OUTx</sub> =0.5A, DIAG_EN falling edge to V <sub>CS</sub> falling                                         | 2 10   | ) uS |

| tcs_on(IN)                | CS settling time from IN rising edge                 | DIAG_EN=5V, I <sub>OUTx</sub> =0.5A, INx rising edge to V <sub>CS</sub> rising                                   | 100 16 | 0 uS |

| tcs_off(IN)               | CS settling time from IN falling edge                | DIAG_EN=5V, I <sub>OUTx</sub> =0.5A, INx rising edge to V <sub>CS</sub> rising                                   | 3 10   | ) uS |

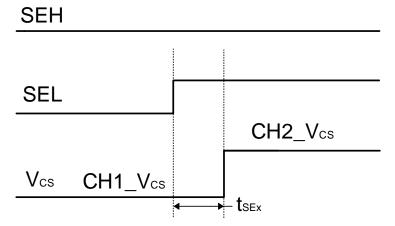

| tsex                      | Multi-sense transition delay from channel to channel | DIAG_EN=5V,Current sense output<br>delay when multi-sense pins SEL and<br>SEH transition from channel to channel | 100    | uS   |

Figure 1. Output And CS Delay Sequential

Figure 2. Open Load Delay

Figure 3. Multi-Sense Transition Delay

## TYPICAL CHARACTERISTICS

Figure 4. INx Threshold VS Temperature

Figure 6. Drain-to-Source Clamp Voltage VS Temperature

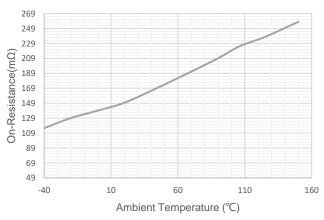

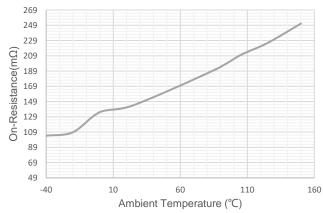

Figure 8. Channel-1 FET On-Resistance VS Temperature

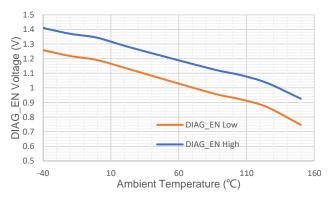

Figure 5. DIAG\_EN Threshold VS Temperature

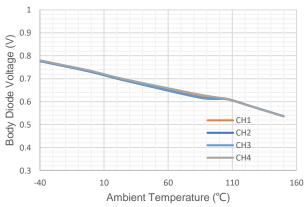

Figure 7. Body-Diode Forward Voltage VS Temperature

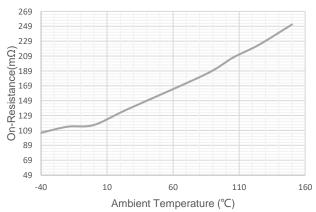

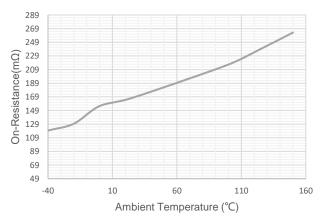

Figure 9. Channel-2 FET On-Resistance VS Temperature

## TYPICAL CHARACTERISTICS

Figure 10. I<sub>SHUTDOWN</sub> vs Input Voltage

Figure 11. I<sub>Q</sub> vs Input Voltage

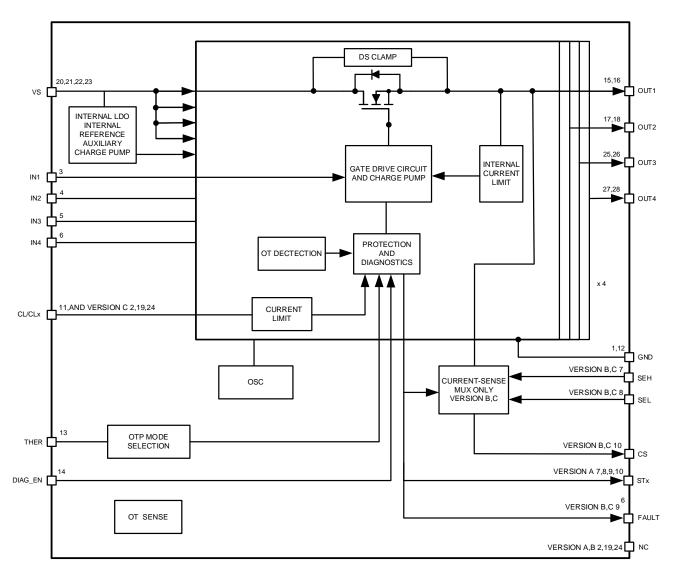

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 12. Functional Block Diagram

#### **OPERATION**

#### Overview

SCT44160Q is a four-channel intelligent high-side switch that internally integrates a charge pump and four power N-MOSFETs. SCT44160Q offers external adjustable threshold overcurrent protection functionality, with a typical value of 7A for internal current limiting to enhance design flexibility and system reliability. This device features comprehensive diagnostic functions and high-precision current sensing functions to achieve smart control of the load. Among SCT44160Q's three versions, Version A includes an open-drain digital output diagnostic mode. Version B provides current sensing analog output. Version C provides four external adjustment functions for overcurrent thresholds based on version B.

In Version A, an open-drain digital output is utilized, and the diagnostic output pin STx needs to be pulled down to the ground externally by providing a pull-up voltage of 3.3V or 5V to match the MCU. The abnormal status of each channel in version A can be reported separately to help the system quickly locate problematic channels.

Version B has a current sensing analog output, enabling the system to accurately determine the operational status of each channel. The integrated current mirror of the device provides a mirror current of 1/Kcs load current, which flows through the CS resistor and becomes a voltage signal to achieve analog output of load current. Version B can achieve the current information detection function for each channel through cyclic selection of SEH SEL pins. Additionally, in the event of an abnormality in a specific channel, the global diagnostic function of the Fault pin can be employed to pinpoint the problematic channel.

The diagnostic function of version C is consistent with version B, but version C can set four overcurrent thresholds separately. Four overcurrent thresholds can be reasonably set according to the application environment, further improving the flexibility and reliability of system design.

SCT44160Q has a clamping function between the drain and source electrodes, which can effectively protect itself under inductive load conditions.

SCT44160Q is an intelligent high-side switch suitable for applications where resistance, capacitance, and inductance loads can support most small load currents.

#### **Adjustable Current Limit**

SCT44160Q has an adjustable high-precision current limitation mechanism. When the load current reaches the designated threshold, it rapidly internally controls the N-MOSFET gate voltage to clamp the output current to the set value and report faults. When overcurrent occurs, there is high power dissipation in the device. If the device heats up and triggers thermal shutdown, the current limit will be reduced to I<sub>CL (TSD)</sub> to reduce power dissipation on the device and further protect the device.

SCT44160Q has two overcurrent protection thresholds, internal and external.

Internal current limitation, SCT44160Q has a conventional value of 7A for internal integrated current limitation. When the CL/CLx pin is connected to the IC GND, the external current limitation becomes inactive, and protection is solely managed by the internal current limitation. This configuration is generally suitable for applications involving low VS voltage transient high current instances. At this point, there is a certain application risk when VS is under high voltage.

External adjustable current limit, SCT44160Q can set the current limit threshold through an external R<sub>CL</sub> resistor, which needs to be connected between CL and IC GND. Use Equation 1 to calculate the RCL resistance:

$$R_{CL} = \frac{V_{CL} \times K_{CL}}{I_{Limit}} \tag{1}$$

#### Where

- V<sub>CL</sub> is an internal reference value with a typical value of 0.8V

- K<sub>CL</sub> is a typical value of 2700 for the load current sampling ratio

#### **Accurate Current Sense**

Version B and version C have high-precision current detection functions, which can accurately detect the real-time status of each channel, making it convenient for the system to accurately diagnose the status of each channel. Version B and version C internally integrate a current mirror to mirror the load current. The ratio between the load current and the mirror current is Kcs: 1, and the mirror current flows through the CS pin and an external ground resistor R<sub>CS</sub>, generating a voltage signal to achieve load current detection. The current mirror is shared among all four channels, with mirror channel selection achieved through the SEH and SEL pins to realize current detection functionality for each channel. Refer to Formula (2) for RCS calculation:

$$R_{CS} = \frac{V_{CS} \times K_{CS}}{I_{OUTY, MAX}} \tag{2}$$

#### Where

- Vcs is the voltage value corresponding to the maximum load current, the values should refer in the EC table to Vcs LIN range

- K<sub>CS</sub> stands for the load current sampling mirror ratio, typically set to 300.

- I<sub>OUTX</sub> MAX represents the maximum load current value for the current channel.

When the system malfunctions, CS will pull up to V<sub>CS\_H</sub> cooperates with the Fault pin for fault detection. Through SEH and SEL pin selection, the faulty channel can be pinpointed. At this point, in order to make the fault detection judgment effective, there are limitations in equation (3) for the R<sub>CS</sub>:

$$R_{CS} \ge \frac{V_{CS\_H(MIN)}}{I_{CS\_H(MIN)}} \tag{3}$$

#### Where

- V<sub>CS</sub> H (MIN) is the minimum value of VCS

- ICS H (MIN) is the minimum value of ICS

#### **Diagnostic Enable Function**

Through DIAG\_ EN pin can set the device to enable or disable diagnostic functions. The diagnostic function is enabled when the DIAG EN is high, and disabled when the DIAG EN is low. When the diagnostic function is disabled, it will reduce the standby power consumption of the device.

#### **Multiplexing of Current Sense**

In versions B and C, multiplexing of four-channel current detection and fault reporting can be achieved through changes in SEH and SEL pin levels. Specific selection and use of Table 1

Table 1 Diagnosis Configuration Table

| Table 1. Diagnosis Comigaration Table |     |     |                   |  |  |  |  |  |

|---------------------------------------|-----|-----|-------------------|--|--|--|--|--|

| DIAG_EN                               | SEH | SEL | CS Mirror Channel |  |  |  |  |  |

|                                       | 0   | 0   | Channel 1         |  |  |  |  |  |

| Н                                     | 0   | 1   | Channel 2         |  |  |  |  |  |

|                                       | 1   | 0   | Channel 3         |  |  |  |  |  |

|                                       | 1   | 1   | Channel 4         |  |  |  |  |  |

#### STx and FAULT Reporting

Version A, all four channels have corresponding STx pins for fault reporting. Pulling down the internal STx device to GND requires the external pull-up, with conventional values of 3.3V and 5V. When a channel malfunctions, the corresponding STx pin will be pulled down to GND, so that the system can guickly detect the faulty channel.

Version B and version C, the FAULT pin is used for global fault reporting. The internal pull-down of the faulty device to GND requires the external pull-up, with conventional values of 3.3V and 5V. When any channel malfunctions, the FAULT pin will be pulled down to GND. After reporting the fault, the MCU can use the SEH and

SEL pins for multi-channel current detection and fault report multiplexing, and select the corresponding channel of the CS pin to read whether the voltage of the CS pin is  $V_{CS\_H}$  determines the channel where the fault occurred. The fault report is shown in Table 2:

| Tab  | le 2 | Fault  | Table  |

|------|------|--------|--------|

| I ab |      | ı auıı | I abic |

| Conditions                                    | INx | OUTx | Criterion               | STx | CS                  | FAULT |

|-----------------------------------------------|-----|------|-------------------------|-----|---------------------|-------|

| Normal                                        | L   | L    | -                       | Н   | 0                   | Н     |

|                                               | Н   | Н    | -                       | Н   | In linear<br>region | Н     |

| Overlaod, short to ground                     | Н   | L    | Current limit triggered | L   | Vcs_H               | L     |

| Open load, short to battery, reverse polarity | L   | Н    | VVS – VOUTx < V(ol,off) | L   | V <sub>CS_H</sub>   | L     |

| Thermal shutdown                              | Н   | -    | TSD triggered           | L   | Vcs_H               | L     |

## **Open-Load Detection**

There are two types of load open circuit detection:

- 1. When INx is low, the channel is turned off, and due to the open circuit of the load, the OUTx voltage cannot decrease rapidly. When the OUTx voltage and power supply voltage still meet V<sub>VS</sub> V<sub>OUTx</sub><V<sub>OL\_OFF</sub> after t<sub>DOL\_OFF</sub>, then an open load condition is determined, and STx/FAULT reports the fault. Due to potential leakage currents and external components, it is generally recommended to use a pull-up resistor between VS and OUTx to offset leakage current, ensuring a more accurate open load report. The recommended value for pull-up resistance is 10k.

- 2. When INx is high, the high-precision current detection function of version B and version C can be used when the channel is turned on. When the V<sub>CS</sub> voltage is detected to be too low, it can be considered that the corresponding channel load is open.

Figure 12. Open-Load Detection

#### **Loss-of-GND Protection**

SCT44160Q features Loss-of-GND protection. By connecting the DIAG\_EN or THER pin to external ground (THER is typically recommended), in case of a loss of ground, the status is determined by the voltage difference

between IC GND and the DIAG\_EN or THER pin connected to external ground. Regardless of whether INx is high or low, the channels will be deactivated for protection.

#### Thermal Shutdown

Under extreme conditions like overcurrent, the device undergoes substantial power stress and heats up rapidly. SCT44160Q incorporates two types of thermal protection: absolute thermal protection and relative thermal protection. These are designed to prevent rapid overheating of the device without protection.

When absolute overheating occurs, the thermal shutdown will be triggered, and the behavior after thermal shutdown can be determined by configuring THER:

- 1. When the THER pin is low, thermal shutdown enters automatic restart mode. After triggering the thermal shutdown, when TJ<T<sub>SD</sub>-T<sub>HYS</sub>, the output will recover, but the current limit threshold will be reduced to 40% of the design value, reducing power stress and enhancing protection. When TJ<T<sub>SD\_RST</sub> or related INx pin restart thermal fault signal will be cleared.

- 2. When THER pin is high, thermal shutdown enters latch mode. After the thermal shutdown, the output will be locked, and the channel will be deactivated. The thermal fault signal from the relevant INx pin is cleared, or switching the THER pin level to ground will transition the thermal shutdown into automatic restart mode.

#### **Inductive-Load Switching-Off Clamp**

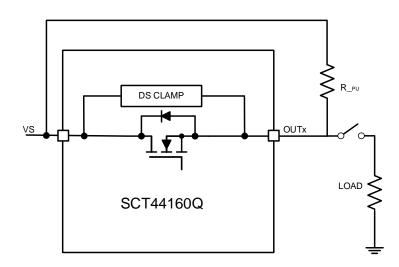

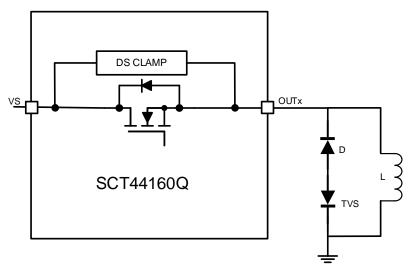

When disconnecting the inductive load, the output will be pulled negative due to the influence of the induced electromotive force. At this time, the VS voltage is still positive, and excessive output negative voltage may cause power MOSFET voltage breakdown. To protect the device, the SCT44160Q internally integrates a voltage clamp function, namely  $V_{DS \, (clamp)}$ . When the output negative voltage is too large, the voltage between  $V_{VS}$  and  $V_{OUTx}$  will be clamped to  $V_{DS \, (clamp)}$  to protect the power MOSFET. When the energy of the inductive load is too large, it is recommended to use the method shown in Figure 13 for further protection.

Figure 13. Inductive Load External Protection Circuit

For more information www.silicontent.com © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

## APPLICATION INFORMATION

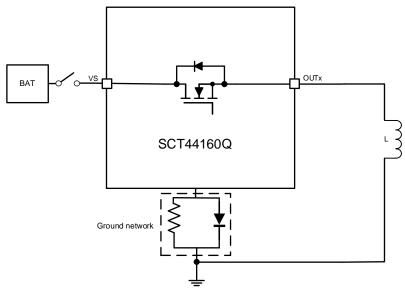

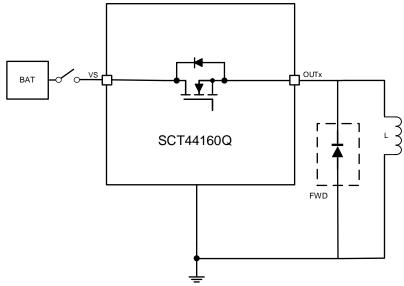

#### **Protection for Loss of Power Supply**

There is no risk for resistive or capacitive loads when the input power supply suddenly disconnects. However, for inductive loads, sudden changes in inductance current will generate induced electromotive force. It is recommended to add a GND network or external freewheeling diode to prevent excessive energy from damaging the chip. Join GND network THE and DIAG\_ EN cannot be grounded to prevent ground failure error reporting.

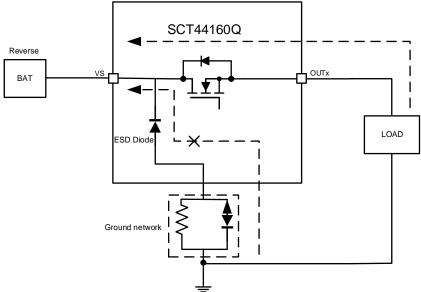

Figure 14. Ground Network Power Loss Protection

Figure 15. The Freewheeling Diode Power Loss Protection

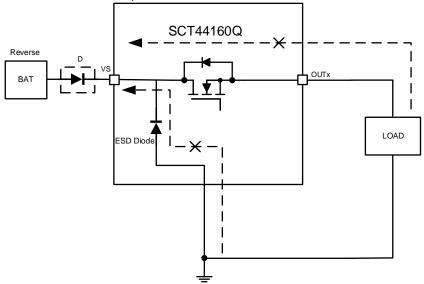

#### **Reverse-Current Protection**

When there is an input short circuit, the reverse current flows to the input through the body diode, and when the input polarity is reversed, the reverse current flows to the input through GND and the body diode. Since the current-handling capacity of the GND pin is limited, for device protection, it's advisable to include a reverse

protection diode at the input or incorporate it into the GND network. When a reverse protection diode is added to the input, both the load and the device are protected.

Figure 16. Anti Reverse Diode Power Reverse Protection

By adding to the GND network, the current flowing into IC GND will be limited, thus protecting the device.

Figure 17. Ground Network Power Reverse Protection

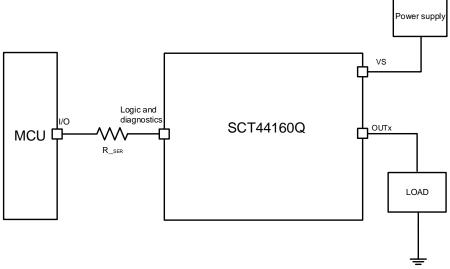

#### **MCU I/O Protection**

In some extreme cases, such as ISO7637-2 testing or inductive load input disconnection, negative voltage pulses may appear in the IC GND relative to the system ground. To protect the MCU and the device, it is recommended to connect a series resistor between the MCU and the SCT44160Q logic control pin.

Figure 18. MCU I/O Protection

## **Typical Application**

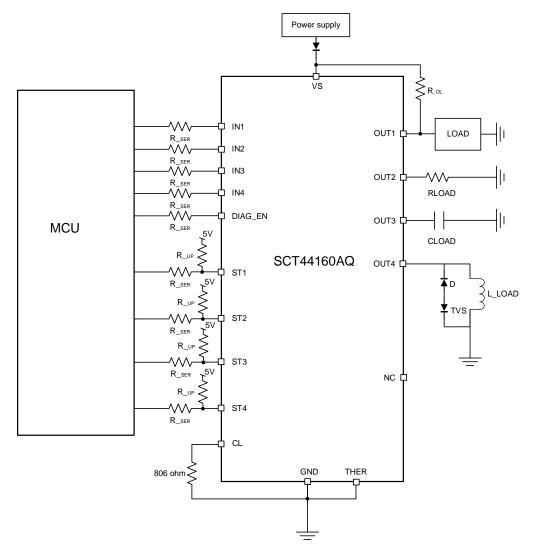

Figure 19. Version A Application Schematic

**Design Parameters**

| Design Parameters | Example Value          |  |  |  |

|-------------------|------------------------|--|--|--|

| Input Voltage     | 13.5V Normal 8V to 18V |  |  |  |

| Load Current      | Typical 1A             |  |  |  |

| Current Limit     | 2.5A                   |  |  |  |

| MCU Voltage       | 5V                     |  |  |  |

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved Product Folder Links: SCT44160Q

## **Typical Application (continued)**

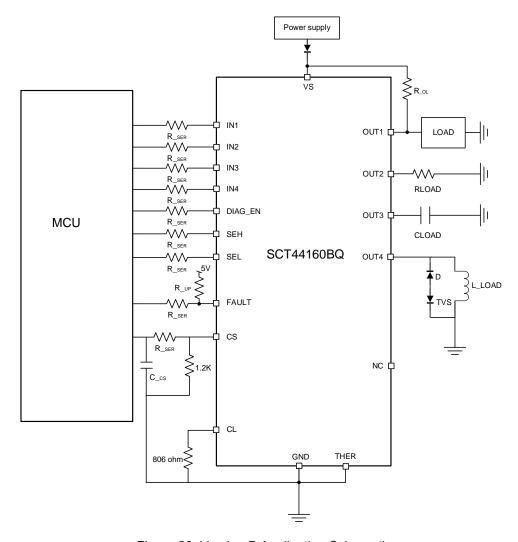

Figure 20. Version B Application Schematic

**Design Parameters**

| Design Parameters   | Example Value          |  |

|---------------------|------------------------|--|

| Input Voltage       | 13.5V Normal 8V to 18V |  |

| Load Current        | Typical 1A             |  |

| Current Limit       | 2.5A                   |  |

| MCU Voltage         | 5V                     |  |

| Current Sense Range | 0-1A                   |  |

## **Typical Application (continued)**

Figure 21. Version C Application Schematic

**Design Parameters**

| Design Parameters   | Example Value          |

|---------------------|------------------------|

| Input Voltage       | 13.5V Normal 8V to 18V |

| Load Current        | Typical 1A             |

| CH1 Current Limit   | 2.5A                   |

| CH2 Current Limit   | 2A                     |

| CH3 Current Limit   | 1.5A                   |

| CH4 Current Limit   | 2A                     |

| MCU Voltage         | 5V                     |

| Current Sense Range | 0-1A                   |

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved Product Folder Links: SCT44160Q

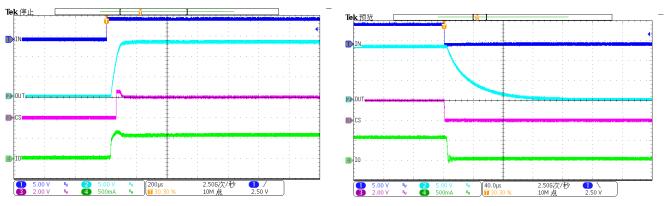

## **Application Waveforms**

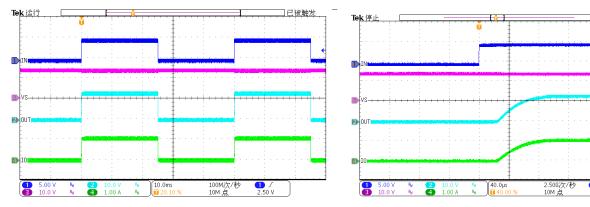

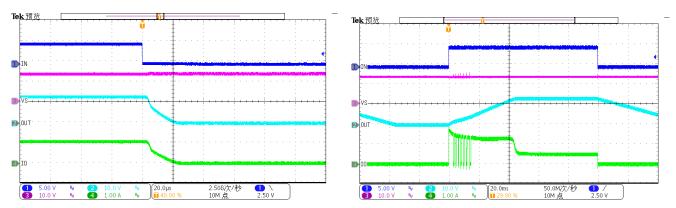

V<sub>VS</sub>=13.5V, unless otherwise noted

Figure 22. IN Toggle resistive load 1A

Figure 23. IN On resistive load 1A

Figure 24. IN Off resistive load 1A

Figure 25. IN Toggle capacitive load C=2.2mF

Figure 26. IN Off Inductive load L=8mH series resistor=13.5 $\Omega$

Figure 27. Open-load detection

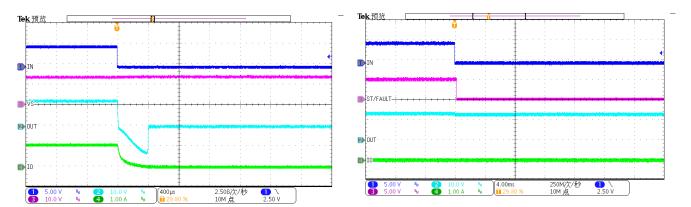

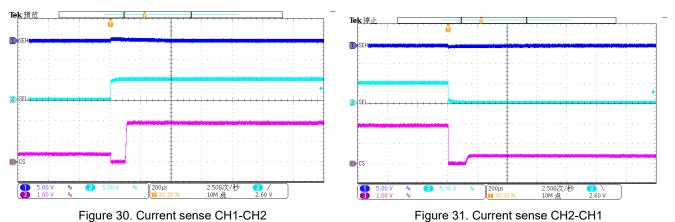

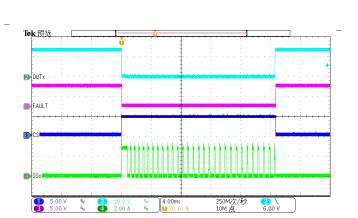

## **Application Waveforms(continued)**

V<sub>VS</sub>=13.5V, unless otherwise noted

Figure 28. IN On current sense load=0.5A

Figure 29. IN Off current sense load=0.5A

Figure 30. Current sense CH1-CH2

Figure 32. Overcurrent detection for version A

Figure 33. Overcurrent detection for version B/C

6.00 V

Tek 停止

DUT<sub>X</sub>

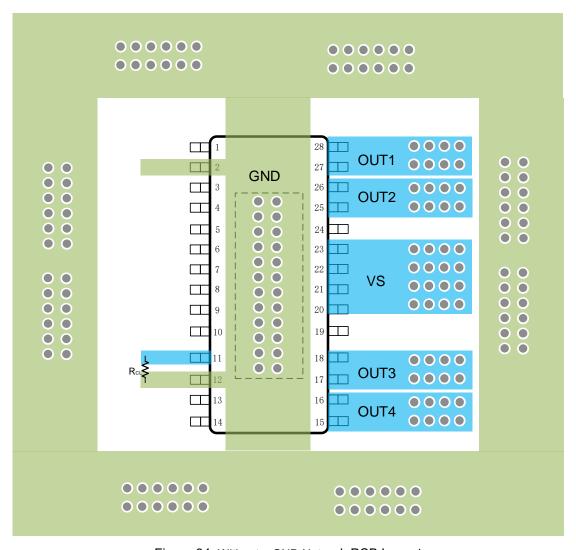

#### **Layout Guideline**

The PCB layout is very important. Good PCB design can optimize heat transfer, which is absolutely essential for the long-term reliability of the device.

- 1. Maximize the copper coverage on the PCB to increase the thermal conductivity of the board. Maximum copper is extremely important when there are not any heat sinks attached to the PCB on the other side of the package.

- 2. More vias should be placed below the device Thermal PAD to further improve heat transfer.

- 3. R<sub>CL</sub> should be connected to IC GND.

Figure 34. Without a GND Network PCB Layout

Figure 35. With a GND Network PCB Layout

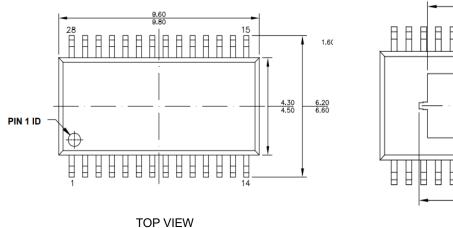

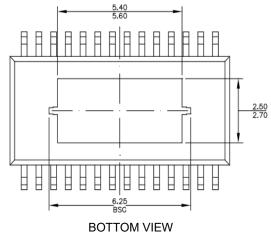

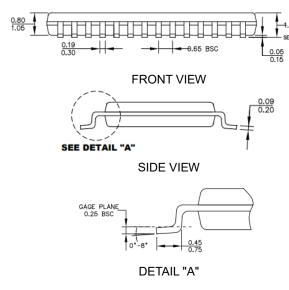

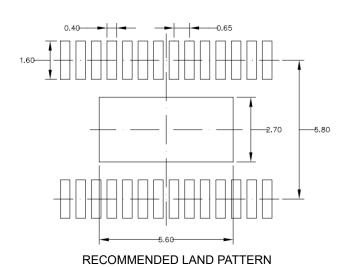

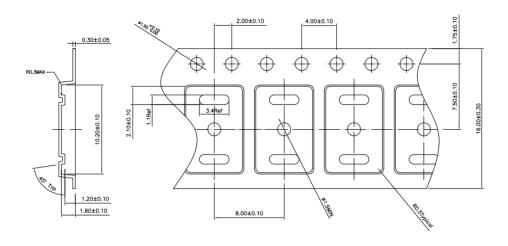

## PACKAGE INFORMATION

#### NOTE:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS..

- 2. PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3. PACKAGE WITDH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5. DRAWING CONFORMS TO JEDEC MO-153, VARIATION ABT.

- 6. DRAWING IS NOT TO SCALE.

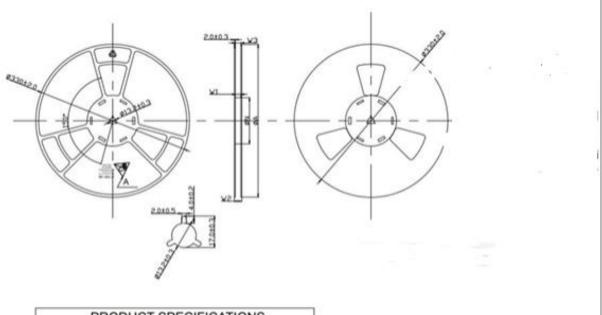

## TAPE AND REEL INFORMATION

| PRODUCT SPECIFICATIONS |         |         |         |         |           |  |

|------------------------|---------|---------|---------|---------|-----------|--|

| TYPE WIDTH             | ØA      | øN      | W1(+00) | W2(Max) | W3(sta)   |  |

| 16MM                   | 330±2.0 | 100±1.0 | 16.4    | 22.4    | 15.9/19.4 |  |

NOTES:

1.10 sprocket hole pitch cumulative tolerance±0.2

2.Camber not to exceed 1mm in 100mm.

3.Material: Black conductive Polystyrene.

4.Ao and Bo measured on a plane 0.3mm above the bottom of the pocket.

5.Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier.

6.Pocket postion raidtive to sprocket hole measured as true postion of pocket, not pocket hole.

7.Pocket center and pocket hole center must be same postion.