# USB Power-Distribution Switch with Fault Blanking

#### **DESCRIPTION**

The EUP3550 is an incorporated power-distribution switch for USB applications and the  $70m\Omega$  P-channel MOSFET realized in this IC.

The EUP3550 integrates several protection features to prevent catastrophic switch failure caused by increasing power dissipation. When the output load exceeds the current-limit threshold or a short is present, the system limits the output current to safe level by switching into a constant-current limit mode and pulls the OCB logic output low. An internal reverse voltage comparator disables the power switch when the output voltage is driven higher than the input to protect devices on the input side of switch.

OCB is open-drain output which is asserted when over-current or over-temperature event occurs. A 8ms fault-blanking feature enables the circuit to ignore momentary faults, such as those caused when hot-swapping a capacitive load, preventing false alarms to the host system. The EUP3550 eliminates any reversed current flow across the switch when it is powered off.

The EUP3550 is available in SOT23-5 and MSOP-8 packages, operates over the extended (-40°C to +85°C) temperature range.

#### **FEATURES**

- $70\text{m}\Omega(\text{typ.})$  Power MOSFET

- Operating Range : 2.7V to 5.5V

- Under Voltage Lockout

- 17μA Quiescent Current

- 1µA Maximum Shutdown Shutdown Current

- No Reverse Current when Power Off

- Fault Blanking Open-Drain Over-Current Flag Output OCB

- Output Shutdown Pull-low Resistor

- Available with 3 Versions of Current Limits with Foldback.

- Enable Active-High or Active-Low

- Available in SOT23-5 and MSOP-8 Packages

- RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

#### **APPLICATIONS**

- USB Ports and Hubs

- TV

- Set-Top Boxes

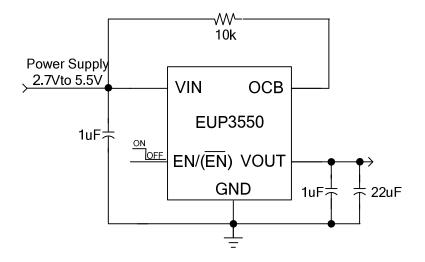

#### **Typical Application Circuit**

Figure 1.

## **Pin Configurations**

| Package Type            | Pin Configurations                             | Package Type            | Pin Configurations                                                  |  |  |

|-------------------------|------------------------------------------------|-------------------------|---------------------------------------------------------------------|--|--|

| SOT23-5<br>EUP3550A1/B1 | Top View VIN EN/(EN)  5 4  1 2 3  VOUT GND OCB | SOT23-5<br>EUP3550A2/B2 | Top View VOUT VIN  5 4  1 2 3  EN/(EN) GND OCB                      |  |  |

| SOT23-5<br>EUP3550A3/B3 | Top View EN/(EN)  5 4  1 2 3  VOUT GND VIN     | MSOP-8<br>EUP3550A/B    | Top View  GND 1 8 VOUT  VIN 2 7 VOUT  VIN 3 6 VOUT  EN/(EN) 4 5 OCB |  |  |

## **Pin Description**

| NAME             | SOT23-5<br>A1/B1 | SOT23-5<br>A2/B2 | SOT23-5<br>A3/B3 | MSOP-8<br>A/B | DESCRIPTION                                                                                                                                                                                                      |  |  |  |

|------------------|------------------|------------------|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>OUT</sub> | 1                | 5                | 1,5              | 6,7,8         | Power Output. Bypass V <sub>OUT</sub> to GND with a 1uF ceramic capacitor. Load conditions might require additional bulk capacitance.                                                                            |  |  |  |

| GND              | 2                | 2                | 2                | 1             | <b>Ground</b> . The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                              |  |  |  |

| ОСВ              | 3                | 3                |                  | 5             | Fault Indicator Output. Open-drain output asserts low when enters thermal shutdown, or a sustained (8ms typical) current-limit or short-circuit condition.                                                       |  |  |  |

| ( EN/<br>( EN )  | 4                | 1                | 4                | 4             | Enable: Logic level enable input. Make sure EN/( EN ) pin never floating.  EN : Logic high turns on power switch. EN : Logic low turns on power switch.                                                          |  |  |  |

| $V_{\rm IN}$     | 5                | 4                | 3                | 2,3           | Power Input. Connect all $V_{\rm IN}$ inputs together and bypass with a 1uF or greater ceramic capacitor to GND. Load conditions might require additional bulk capacitance to prevent pulling $V_{\rm IN}$ down. |  |  |  |

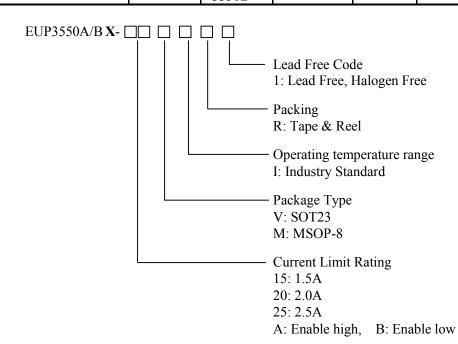

## **EUP3550**

## **Ordering Information**

| Order Number     | Package<br>Type | Marking        | ENABLE     | Current<br>Limit | OCB Output | Quantity<br>per Reel | Operating<br>Temperature<br>Range |

|------------------|-----------------|----------------|------------|------------------|------------|----------------------|-----------------------------------|

| EUP3550A1-20VIR1 | SOT23-5         | xxxxx<br>Ba20  | Logic High | 2A               | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550A2-20VIR1 | SOT23-5         | xxxxx<br>Bb20  | Logic High | 2A               | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550A3-20VIR1 | SOT23-5         | xxxxx<br>Bc20  | Logic High | 2A               | NO         | 3000                 | -40 °C to +85°C                   |

| EUP3550B1-20VIR1 | SOT23-5         | xxxxx<br>Bd20  | Logic Low  | 2A               | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550B2-20VIR1 | SOT23-5         | xxxxx<br>Be20  | Logic Low  | 2A               | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550B3-20VIR1 | SOT23-5         | xxxxx<br>Bf20  | Logic Low  | 2A               | NO         | 3000                 | -40 °C to +85°C                   |

| EUP3550A1-15VIR1 | SOT23-5         | xxxxx<br>Ba15  | Logic High | 1.5A             | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550A2-15VIR1 | SOT23-5         | xxxxx<br>Bb15  | Logic High | 1.5A             | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550A3-15VIR1 | SOT23-5         | xxxxx<br>Bc15  | Logic High | 1.5A             | NO         | 3000                 | -40 °C to +85°C                   |

| EUP3550B1-15VIR1 | SOT23-5         | xxxxx<br>Bd15  | Logic Low  | 1.5A             | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550B2-15VIR1 | SOT23-5         | xxxxx<br>Be15  | Logic Low  | 1.5A             | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550B3-15VIR1 | SOT23-5         | xxxxx<br>Bf15  | Logic Low  | 1.5A             | NO         | 3000                 | -40 °C to +85°C                   |

| EUP3550A-25MIR1  | MSOP-8          | xxxxx<br>3550A | Logic High | 2.5A             | YES        | 3000                 | -40 °C to +85°C                   |

| EUP3550B-25MIR1  | MSOP-8          | xxxxx<br>3550B | Logic Low  | 2.5A             | YES        | 3000                 | -40 °C to +85°C                   |

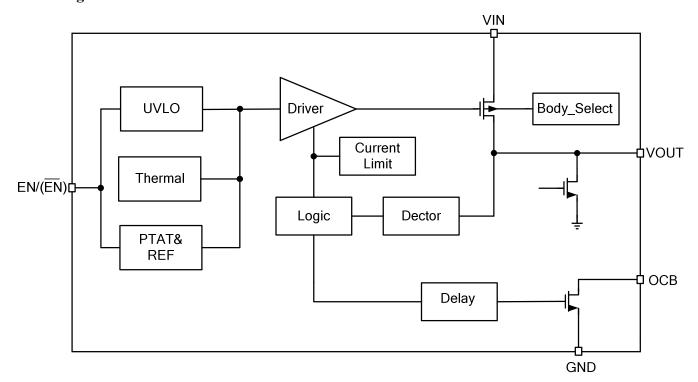

## **Block Diagram**

Figure 2.

-40°C to +85°C

### **Absolute Maximum Ratings (1)**

| ■ Supply Voltage (V <sub>IN</sub> )                  |                |

|------------------------------------------------------|----------------|

| ■ Output Voltages (V <sub>OUT</sub> )                | 6V             |

| ■ Output Current (I <sub>OUT</sub> ) Inte            | rnally Limited |

| $lacktriangle$ Enable Input $(V_{EN})$               | -0.3V to 6V    |

| $\blacksquare$ Storage Temperature (T <sub>S</sub> ) | -65°C to 150°C |

| ■ Reflow Temperature (soldering, 10sec)              | 260°C          |

| ■ Thermal Resistance $\theta_{JA}$ (SOT23-5)         | 205°C /W       |

| <b>Recommend Operating Conditions (2)</b>            |                |

| ■ Supply Voltage (V <sub>IN</sub> )                  | 2.7V to 5.5V   |

Note (1): Stress beyond those listed under "Absolute Maximum Ratings" may damage the device.

Note (2): The device is not guaranteed to function outside the recommended operating conditions.

#### **Electrical Characteristics**

Unless otherwise specified,  $V_{IN}$ =5V,  $C_{IN}$ = $C_{OUT}$ =1 $\mu$ F,  $T_A$ =+25°C.

Operating Temperature (T<sub>A</sub>)

| Symbol                | Parameter                                | Conditions                                | EUP3550 |      |      | Units |  |

|-----------------------|------------------------------------------|-------------------------------------------|---------|------|------|-------|--|

| Symbol                | 1 at affected                            | Conditions                                | Min.    | Тур. | Max. | Onics |  |

| $V_{IN}$              | Operating Voltage                        |                                           | 2.7     |      | 5.5  | V     |  |

| R <sub>ON</sub>       | Output MOS R <sub>DS(ON)</sub>           | IC Enable, I <sub>OUT</sub> =1A           |         | 70   |      | mΩ    |  |

| $I_Q$                 | Supply Current                           | IC Enable                                 |         | 16   | 25   | μΑ    |  |

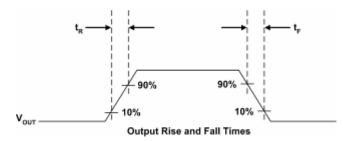

| T <sub>RISE</sub>     | Output Turn-on Rising Time               |                                           |         | 350  |      | us    |  |

|                       |                                          | V <sub>OUT</sub> =4V, EUP3550X – 15VIR1   | 1.2     | 1.5  | 1.8  |       |  |

| $I_{LIMIT}$           | Current Limit Threshold                  | V <sub>OUT</sub> =4V, EUP3550X – 20VIR1   |         | 2.0  |      | Α     |  |

|                       |                                          | V <sub>OUT</sub> =4V, EUP3550A/B – 25MIR1 |         | 2.5  |      |       |  |

| I <sub>SHORT</sub>    | Short-Circuit Current                    | V <sub>OUT</sub> =0V                      |         | 0.8  |      | Α     |  |

| $V_{\rm IL}$          | Low-Level Input Voltage                  |                                           |         |      | 0.8  | V     |  |

| V <sub>IH</sub>       | High-Level Input Voltage                 |                                           | 2       |      |      | V     |  |

| I <sub>SHDN</sub>     | Shutdown Supply Current                  | IC Disable                                |         | 0.4  | 1    | μΑ    |  |

| $R_{SHDN}$            | Shutdown Pull Low Resistance             |                                           |         | 30   |      | Ω     |  |

| $I_{LEAK}$            | Output Leakage Current                   | IC Disable, V <sub>OUT</sub> =0V          |         | 0    | 1    | μΑ    |  |

| $V_{\rm UVLO}$        | V <sub>IN</sub> Under Voltage Lockout    |                                           | 1.3     | 1.5  | 1.7  | V     |  |

| V <sub>UVLO-Hys</sub> | V <sub>IN</sub> Under Voltage Hysteresis |                                           |         | 200  |      | mV    |  |

| T <sub>OCB</sub>      | OCB Deglitch                             |                                           | 6       | 8    | 12   | ms    |  |

| V <sub>OCB</sub>      | OCB Output Low Voltage                   | IOCB= 5mA                                 |         |      | 0.2  | V     |  |

| I <sub>OCB</sub>      | OCB Off-State Current                    | VOCB= 5V                                  |         |      | 1    | μΑ    |  |

| TSD                   | Thermal Limit                            |                                           |         | 135  |      | °C    |  |

| TSDH                  | Thermal Limit Hysteresis                 |                                           |         | 20   |      | °C    |  |

#### **Functional Description**

#### **Input and Output**

$V_{\rm IN}$  (input) is the power supply connection to the logic circuitry and the source of the power MOSFET.  $V_{\rm OUT}$  (output) is the drain of the power MOSFET. In a typical application, current flows through the switch from  $V_{\rm IN}$  to  $V_{\rm OUT}$  toward the load. All  $V_{\rm OUT}$  pins must connect together to the load.

#### **Current Limiting**

The EUP3550 continuously monitors the output current for over-current protection to protect the system power, the power switch, and the load from damage during output short circuit .Under over-current condition, the device maintains a constant output current and reduces the output voltage accordingly. Complete shutdown occurs only if the fault is presented long enough to activate thermal limiting. There are several possible over-current conditions can occur.

- The output has been shorted before the device is enabled or before V<sub>IN</sub> has been applied, the EUP3550 senses the short immediately switches into a constant-current limit mode.

- A short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for a short period of time before the current-limit circuit can react. After the current limit circuit has tripped (reached the over-current trip threshold), the device switches into constant current mode.

- The load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current limit threshold is reached or until the thermal limit of the device is exceeded. The EUP3550 is capable of delivering current up to the current limit threshold without damaging the device. Once the threshold has been reached, the device switches into its constant current mode.

The current limit value refers to typical operating characteristics.

#### Thermal Shutdown

Thermal shutdown protector is built in EUP3550. When the die temperature exceeds 135°C, the MOSFETS switch is shut off. 20°C of hysteresis prevents the switch from turning on until the die temperature drops to 115°C. Thermal shutdown circuit functions only when the switch is enabled.

#### **Under-Voltage Lockout**

A voltage-sense circuit monitors the input voltage. When the input voltage falls below approximately 1.3V, the power switch is quickly turned off. The UVLO also keeps the switch from being turned on until the power supply has reached at least 1.5V, even if the switch is enabled.

#### **OCB** Function

The OCB open-drain output is pull low voltage, when an over current condition is encountered over approximately 8ms fault-blanking timeout (to eliminate false over-current reporting). This feature allows the device to handle USB loads that might not be fully compliant with USB specifications. The EUP3550 successfully powers USB loads with additional bypass capacitance and/or large startup currents while protecting the upstream power source. No fault is reported if the switch brings up the load within the 8ms blanking period.

#### **Application Information**

#### **Input Power Supply and Capacitance**

A  $1\mu F$  bypass capacitor from VIN to GND, located near the EUP3550, is strongly recommended to prevent the input voltage dropping during hot-plug events. When the devices is powered by long leads or PC traces ,it is quit to driver inductive loads or operate from inductive sources, larger input bypass capacitance is required to prevent voltage spikes from exceeding the EUP3550's absolute maximum ratings (VIN<sub>MAX</sub> = 6V) during short-circuit events.

#### **Output Capacitor**

A  $1\mu F$  ceramic capacitor between VOUT and GND is recommended to reduce the voltage droop, when the output load is heavy. This precaution reduces power-supply transients that may cause ringing on the input and reduces output voltage transients under dynamic load conditions. Using output capacitors greater than  $470\mu F$  might assert OCB if the current limit cannot charge the output capacitor within the 8ms fault-blanking period.

#### EN, the Enable Logic Input

EN must be driven logic low or logic high for a clearly defined input. Floating the input may cause unpredictable operation. EN should not be allowed to go negative with respect to GND.

#### **Driving Inductive Loads**

To the USB port with cables is typically connected A wide variety of devices (mice, keyboards, cameras, and printers), which might add an inductive component to the load. This inductance causes the output voltage at the USB port to oscillate during a load step. The EUP3550 drives inductive loads, but avoid exceeding the device's absolute maximum ratings. Usually, the load inductance is relatively small, and the EUP3550's input includes a substantial bulk capacitance from an upstream regulator as well as local bypass capacitors, limiting overshoot.

#### **Layout and Thermal Dissipation**

Keep all traces as short as possible to reduce the effect of undesirable parasitic inductance and optimize the switch response time to output short circuit conditions. Place input and output capacitors no more than 5mm from device leads. Connect  $V_{\rm IN}$  and  $V_{\rm OUT}$  to the power bus with short traces. Wide power bus planes at  $V_{\rm IN}$  and  $V_{\rm OUT}$  provide superior heat dissipation as well.

An active switch dissipates little power with minimal change in package temperature. Calculate the power dissipation for this condition as follows:

$$P = I_{OUT}^2 \times R_{(DS)ON}$$

At the normal operating current ( $I_{OUT} = 1.5A$ ) and the maximum on resistance of the switch ( $70m\Omega$ ), the power dissipation is:

$$P = (1.5A)^2 \times 0.07\Omega = 158 \text{mW}$$

The worst-case power dissipation occurs when the output current is just below the current limit threshold (2.5A max) with a low output voltage 1V, for example. For a 5V input, the power dissipated is the voltage drop across the switch multiplied by the current limit:

$$P = I_{LIM} \times (V_{IN} - V_{OUT}) = 2.5A \times (5V - 1V) = 10W$$

In this case, the EUP3550 die temperature exceeds the 135°C thermal shutdown threshold, and the switch output shuts down until the junction temperature cools by 20°C. The duty cycle and period are strong functions of the ambient temperature and the PC board layout (see the Thermal Shutdown section). If the output current exceeds the current limit threshold, the EUP3550 asserts a fault state after 8ms.

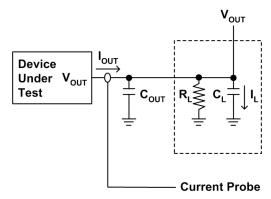

#### **Test Circuit**

Figure 3.

#### **Timing Diagrams**

Figure 4.

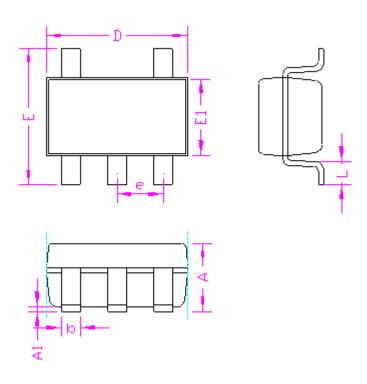

# **Packaging Information**

SOT23-5

| SYMBOLS | MILLIMETERS |        |      | INCHES    |        |       |  |

|---------|-------------|--------|------|-----------|--------|-------|--|

|         | MIN.        | Normal | MAX. | MIN.      | Normal | MAX.  |  |

| A       | -           | -      | 1.40 | -         | -      | 0.055 |  |

| A1      | 0.00        | 1      | 0.15 | 0.000     | -      | 0.006 |  |

| D       | 2.65        | 2.90   | 3.15 | 0.104     | 0.114  | 0.124 |  |

| E1      | 1.40        | 1.60   | 1.80 | 0.055     | 0.063  | 0.071 |  |

| Е       | 2.60        | 2.80   | 3.00 | 0.102     | 0.110  | 0.118 |  |

| L       | 0.30        | 0.45   | 0.60 | 0.012     | 0.018  | 0.024 |  |

| b       | 0.30        | -      | 0.50 | 0.012     | -      | 0.020 |  |

| e       | 0.95 REF    |        |      | 0.037 REF |        |       |  |